## The Specification and Execution of Heterogeneous Synchronous Reactive Systems

Copyright © 1997 by

Stephen Anthony Edwards

Please cite as

Stephen Anthony Edwards. *The Specification and Execution of Synchronous Reactive Systems*. PhD thesis, University of California, Berkeley, 1997. Available as UCB/ERL M97/31. http://ptolemy.eecs.berkeley.edu/papers/97/sedwardsThesis/

#### Abstract

## The Specification and Execution of Heterogeneous Synchronous Reactive Systems

by Stephen Anthony Edwards

Doctor of Philosophy in Engineering University of California, Berkeley Professor Edward A. Lee, Chair

The need for new languages and paradigms for designing software for embedded computing systems continues to grow as general-purpose microcontrollers become faster and cheaper. Many of these system need precise control over when things happen, yet few languages provide this facility. Another major challenge is handling the growing complexity of these systems.

In this dissertation, I present a new model of computation for embedded system software that is the first to fuse precise control over timing with the ability to build systems from heterogeneous pieces. It combines the synchronous model of time (used in languages such as Esterel) with the hierarchical heterogeneity of the Ptolemy system. Heterogeneity addresses the complexity problem by allowing each subsystem to be designed using the best language.

My two major contributions are the formal semantics of this model and an efficient, predictable execution scheme for it. Dealing with zero-delay feedback loops, a side-effect of the zero-delay assumption needed for synchrony, is the semantic challenge, and I solve it with a fixed-point scheme that guarantees all systems are deterministic by construction. The execution scheme I present is provably correct and eliminates run-time scheduling overhead by making all decisions before the system is run.

I present results that show my model of computation is both efficient and can be used to implement practical systems. It is my hope that these ideas will be used in the future to make designing complex time-critical embedded software easier and less error-prone.

# Contents

|           | Pref | face      |                                | ix |

|-----------|------|-----------|--------------------------------|----|

|           | Ack  | nowled    | gements                        | xi |

| Chapter 1 | Intr | oductio   | n                              | 1  |

|           | 1.1  | Synch     | rony                           | 3  |

|           | 1.2  | Hetero    | geneity                        | 5  |

|           | 1.3  | SR Sy     | stems                          | 6  |

|           |      | 1.3.1     | Challenges of Zero Delay       | 7  |

|           |      | 1.3.2     | Execution                      | 9  |

| Chapter 2 | Spe  | cificatio | n                              | 11 |

|           | 2.1  | Synch     | rony and Finite-State Machines | 11 |

|           | 2.2  | Succir    | ctness                         | 13 |

|           | 2.3  | Synch     | ronous Languages               | 14 |

|           |      | 2.3.1     | Tabular Form                   | 15 |

|           |      | 2.3.2     | State Diagrams                 | 15 |

|           |      | 2.3.3     | The OC Format                  | 17 |

|           |      | 2.3.4     | Argos                          | 18 |

|           |      | 2.3.5     | Esterel                        | 21 |

|           |      | 2.3.6     | Lustre                         | 24 |

|           | 2.4  | Hetero    | geneous Languages              | 26 |

|           |      | 2.4.1     | Kahn Process Networks          | 26 |

|           |      | 2.4.2     | Synchronous Data Flow          | 27 |

|--|

| Chapter 3 | Sem | antics  |                                          | 31  |

|-----------|-----|---------|------------------------------------------|-----|

|           | 3.1 | Motiva  | ation                                    | 32  |

|           |     | 3.1.1   | Denotational Semantics                   | 32  |

|           |     | 3.1.2   | Circuit Simulation                       | 34  |

|           | 3.2 | Mathe   | matical Foundation                       | 38  |

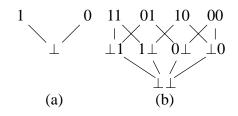

|           |     | 3.2.1   | Complete Partial Orders                  | 39  |

|           |     | 3.2.2   | Monotonic and Continuous Functions       | 43  |

|           |     | 3.2.3   | Least Fixed Points                       | 47  |

|           | 3.3 | The Se  | emantics of SR Systems                   | 49  |

| Chapter 4 | Exe | cution  |                                          | 53  |

|           | 4.1 | Relate  | d Work                                   | 56  |

|           | 4.2 | Findin  | g the Least Fixed Point                  | 58  |

|           |     | 4.2.1   | Iterative Evaluation                     | 59  |

|           |     | 4.2.2   | Chaotic Iteration                        | 62  |

|           |     | 4.2.3   | Series/Parallel Decomposition            | 66  |

|           |     | 4.2.4   | Partitioned Evaluation                   | 67  |

|           |     | 4.2.5   | The Divide-and-Conquer Least Fixed Point |     |

|           |     |         | Algorithm                                | 70  |

|           | 4.3 | Devisi  | ng Efficient Schedules                   | 72  |

|           |     | 4.3.1   | The Minimum Evaluation Cost              | 76  |

|           |     | 4.3.2   | Finding Good Partitions                  | 84  |

|           |     | 4.3.3   | The Branch and Bound Algorithm           | 89  |

|           |     | 4.3.4   | Choosing the Head of an SCC              | 91  |

|           |     | 4.3.5   | Schedule Transformations                 | 92  |

|           |     | 4.3.6   | Experimental Results                     | 95  |

| Chapter 5 | Imp | lementa | ation                                    | 101 |

|           | 5.1 | Ptolem  | ıy                                       | 102 |

|           |     | 5.1.1   | The SR Domain                            | 103 |

|           |     | 5.1.2   | SR Blocks in C++                         | 104 |

|           |     | 5.1.3   | SR Blocks in Itcl                        | 109 |

|           |     | 5.1.4   | SR Blocks from Other Languages           | 111 |

## CONTENTS

|           | 5.2  | A Digi   | tal Address Book                  | 111 |

|-----------|------|----------|-----------------------------------|-----|

|           | 5.3  | A MID    | DI Synthesizer                    | 117 |

|           |      | 5.3.1    | The MIDI Protocol                 | 119 |

|           |      | 5.3.2    | FM Sound Synthesis                | 119 |

|           |      | 5.3.3    | Implementation of the Synthesizer | 123 |

| Chapter 6 | Con  | clusions | 8                                 | 131 |

|           | 6.1  | Implic   | ations of This Work               | 132 |

|           | 6.2  | Future   | Work                              | 135 |

|           |      | 6.2.1    | Execution Issues                  | 135 |

|           |      | 6.2.2    | Language Issues                   | 137 |

|           | Bibl | iograph  | Ŋ                                 | 139 |

|           | Inde | ex       |                                   | 146 |

# List of Definitions and Theorems

| Definition 1        | Partially-ordered set (poset)                             | 39 |

|---------------------|-----------------------------------------------------------|----|

| Definition 2        | Least upper bound                                         | 39 |

| Proposition 1       | Least upper bound is unique                               | 40 |

| Definition 3        | Chain                                                     | 40 |

| Definition 4        | Complete partial order (CPO)                              | 40 |

| Proposition 2       | LUB of a finite chain                                     | 41 |

| Corollary 1         | Poset with finite chains is a CPO                         | 41 |

| Definition 5        | Bottom element                                            | 41 |

| Proposition 3       | Bottom element unique                                     | 41 |

| Proposition 4       | Product space is a CPO                                    | 41 |

| Proposition 5       | Partial order on functions                                | 43 |

| Definition 6        | Monotonic function                                        | 43 |

| Definition 7        | Continuous function                                       | 43 |

| Proposition 6       | Continuous function is monotonic                          | 44 |

| Proposition 7       | Monotonic function with finite chains is continuous       | 44 |

| Proposition 8       | Composition of continuous functions is continuous         | 44 |

| Proposition 9       | Composition of monotonic functions is monotonic           | 45 |

| Proposition 10      | Cross product of continuous functions is continuous       | 45 |

| Proposition 11      | Chains of continuous functions have a least upper bound . | 45 |

| Theorem 1           | Continuous functions form a CPO                           | 46 |

| Definition 8        | Prefixed points, fixed points                             | 47 |

| Theorem 2           | A continuous function on a pointed CPO has a unique least |    |

|                     | fixed point                                               | 48 |

| <b>Definition</b> 9 | Block                                                     | 49 |

| Definition 10       | Connected block                                           | 49 |

## LIST OF DEFINITIONS AND THEOREMS

| Definition | 11 | Open System                                                  | 50 |

|------------|----|--------------------------------------------------------------|----|

| Definition | 12 | SR System                                                    | 50 |

| Lemma      | 1  | The set of all block functions forms a pointed CPO           | 50 |

| Lemma      | 2  | <i>B</i> preserves block functions                           | 52 |

| Lemma      | 3  | <i>B</i> is continuous                                       | 52 |

| Theorem    | 3  | SR Systems are deterministic                                 | 52 |

| Definition | 13 | Height of a CPO                                              | 59 |

| Theorem    | 4  | Height of a product CPO                                      | 60 |

| Corollary  | 2  | Height of a vector is the sum of its components              | 60 |

| Theorem    | 5  | Bounded computation of the least fixed point                 | 61 |

| Definition | 14 | Chaotic Iteration Invariants                                 | 64 |

| Theorem    | 6  | Chaotic Iteration Invariants are true for $\perp$            | 64 |

| Theorem    | 7  | The Chaotic Iteration Invariants are preserved               | 65 |

| Theorem    | 8  | A series/parallel decomposition has the same least fixed     |    |

|            |    | point                                                        | 66 |

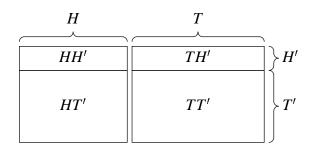

| Theorem    | 9  | Bekić's least fixed point computation                        | 68 |

| Definition | 15 | Separable partition                                          | 69 |

| Corollary  | 3  | Least fixed point of a separable partition                   | 69 |

| Theorem    | 10 | The divide-and-conquer algorithm computes the least fixed    |    |

|            |    | point                                                        | 70 |

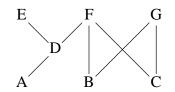

| Definition | 16 | Directed graph                                               | 73 |

| Definition | 17 | Dependency graph                                             | 74 |

| Theorem    | 11 | Evaluation cost is at least linear                           | 78 |

| Theorem    | 12 | Evaluation cost is less than quadratic                       | 78 |

| Corollary  | 4  | Iterative evaluation is non-optimal for non-scalar functions | 80 |

| Theorem    | 13 | Separable partitioning is always optimal                     | 80 |

| Theorem    | 14 | Optimal non-separable partition must be separable            | 83 |

| Definition | 18 | A strongly connected digraph                                 | 84 |

| Definition | 19 | An acyclic digraph                                           | 84 |

| Definition | 20 | Border of a set of vertices                                  | 84 |

| Definition | 21 | A kernel of a graph                                          | 85 |

## LIST OF DEFINITIONS AND THEOREMS

| Theorem    | 15 | A graph is not strongly connected if any only if it has a     |    |

|------------|----|---------------------------------------------------------------|----|

|            |    | kernel                                                        | 85 |

| Theorem    | 16 | A function has a separable partition iff its dependency graph |    |

|            |    | has a kernel                                                  | 85 |

| Definition | 22 | Strongly connected component decomposition                    | 86 |

| Theorem    | 17 | Border sets break strong connectivity                         | 87 |

| Corollary  | 5  | Removing successor sets or predecessor sets breaks strong     |    |

|            |    | connectivity                                                  | 88 |

## Preface

**E**MBEDDED computing systems are everywhere. If you own a VCR, a digital watch, a microwave oven, or an automobile, you probably use them daily without realizing it. This is a mark of good engineering: it solves a problem without calling attention to itself.

This thesis grew from a desire to simplify the task of building these systems. Their growing use of software makes it natural to attack the problem of creating software for these systems. Most of it is currently written using the C language, which was originally designed for operating systems programming. It is a powerful, flexible language, but was not designed for real-time programming where the correctness of a program rests as much on when it performs its function as on what function it performs.

The designers of digital logic (hardware) have long built such timing-critical systems, and their techniques have slowly been creeping into the software world. One of their most powerful paradigms is synchrony, where all parts of a system are synchronized to a periodic clock. Virtually all digital hardware systems use this, and it has recently entered the software world through a group of so-called synchronous languages that includes Esterel, Lustre, and Argos.

Another challenge in designing software systems is handling their complexity. Any reasonable scheme needs to address this, and the heterogeneous approach taken in the Ptolemy system (a system for designing embedded software systems) is one of the more interesting. The basic idea is to treat a system as a collection of black boxes. Within each black box there might be a program, a system, or anything. Carefully choosing the interface to these boxes allows systems built from them to be analyzed and executed without having to understand their contents.

#### PREFACE

The research presented here is the result of combining the idea of synchrony with the Ptolemy approach to heterogeneity. It presents a new model of computation (essentially, a way to assemble systems) that combines both of these ideas. The primary challenge, it turns out, is dealing with instantaneous feedback (the synchronous model is inherently instantaneous, and feedback appears in virtually all interesting systems). The solution I devised follows from results taken from both the programming language semantics community and the circuit simulation community, making it mathematically sound and based on physical principles.

The other big challenge with this approach is actually running the systems. The bulk of this thesis is devoted to making these systems run quickly, predictably, and correctly.

Some of the results in this work can be applied more widely. The problem of dealing with zero-delay feedback in software appears in the two major languages (VHDL and Verilog) currently used to specify hardware systems. Both have failings that could be corrected if some of the techniques presented in this dissertation were adopted. Also, the execution scheme I devised is essentially a very efficient solver for a system of equations. Although many of my techniques are closely tied to the particular domain I chose to work in, I believe the general approach is applicable to similar problems.

> —Stephen Edwards Emeryville, California March 1997

## Acknowledgements

## Advisor: Edward A. Lee

Adnan Aziz Wendell Baker Wan-Teh Chang John Davis II Jerry Edwards Lois Edwards Dan Engels **Brian Evans** Alain Girault Michael Goodwin Lisa Guerra Nina Huang Renu Mehra Praveen Murthy A. Richard Newton Arlindo Oliveira José Luis Pino Rajeev Ranjan H. John Reekie Sanjay Sarma Tom Shiple Gitanjali Swamy

N MY EXPERIENCE, most people read the acknowledgements section of a dissertation to either learn the name of the author's advisor or to see their name in print. For those in a rush, I have summarized this information in the easy-toread list on the left.

For those still reading, here are more detailed comments: Of course, I must begin with my advisor, Edward Lee, without whose help I would never have written this thesis. He gave me just enough direction and advice to get started in the right direction, then got out of my way. I must also thank Richard Newton, my previous advisor, who probably influenced this dissertation more than he or I realize.

Wendell Baker was instrumental in getting me started with synchronous languages in the first place. He also gave me a very useful piece of advice: "your objective should be to write as little code as possible." Eventually (it took a few years), I agreed with him and actually completed this work.

Gitanjali Swamy and her husband, Sanjay Sarma, were both great fun to have around. Gitanjali influenced my attitudes towards CAD research and towards cooking. Sanjay's advice on being an academic will influence me long after I have left Berkeley.

Dan Engels' caustic feedback on an early draft of this dissertation was invaluable. What you are reading was largely shaped by his cynicism. I can hardly wait to return the "favor" when he gets ready to write his dissertation. John Davis also read through an early draft.

Rajeev Ranjan and his wife Renu Mehra also deserve mention, not just because they fed me, but because Renu and her cubiclemate, Lisa

#### <u>ACKNOWLEDGEMENTS</u>

Guerra, were almost completely responsible for getting my qualifying exam presentation into shape.

Tom Shiple's discipline made me realize I still have a long way to go. Discussions with him about Malik's work and asynchronous circuit models greatly clarified my thinking on these matters.

Discussions with Adnan Aziz were a great help, even when they lead to him writing some unintelligible equation on the blackboard, something they always seemed to do. He also made me feel better about my own graduate student angst after explaining his story.

Arlindo Oliveira returned home to Portugal all too soon. He taught me a lot about how to approach research.

José Pino welcomed me warmly into Lee's group, and taught me a lot about the Ptolemy philosophy. He also made me realize that no matter how hard I though graduate school was, it was much harder with four children.

Discussions with John Reekie were always stimulating, assuming he had had enough coffee. Discussions with him about control and dataflow eventually lead to the scheme I present here, and he was a great help when I was building my synthesizer example.

Wan-Teh Chang was an excellent cubiclemate. He only seemed to open his mouth when he had a good suggestion about synchronous languages. Michael Goodwin took over his desk and gave me some good advice about the music synthesis world.

Brian Evans taught me a lot about being an academic. In addition to providing hair styling tips, he perfectly illustrated the attitude one needs to become a professor, inadvertently convincing me not to.

Praveen Murthy helped me work through some of the more sticky mathematical points in this dissertation. Without his help, I fear I would still be stuck.

Alain Girault reinforced my stereotypes of frenchmen. He's arrogant, dismissive, clever, and very helpful. I'll miss his flippant attitude and technical prowess.

#### ACKNOWLEDGEMENTS

Nina Huang was both my greatest inspiration and greatest distraction during this work. I thank her for both—her timing was perfect.

Of course, no acknowledgements section in a dissertation would be complete without some sappy comment about the author's parents, and unfortunately, this one will be no exception. I have a hard time imagining a set of parents who could be more supportive and helpful during such a challenging task. For this, I thank them both (Jerry and Lois Edwards).

## Introduction

Art is solving problems that cannot be formulated before they have been solved. The shaping of the question is part of the answer. —Piet Hein

THE NEED for new languages and paradigms for designing embedded systems continues to grow. The falling cost of hardware has caused both the ubiquity and complexity of these application-specific computing systems to grow, and with more complexity comes a greater need to contain it. In this dissertation, I present a new model of computation—essentially a coordination language for describing the software in these systems. It is the first to combine precise control over when things happen with the ability to assemble systems from pieces described in different languages, a way to fight complexity by allowing each piece to use the most suitable language.

My focus is on *reactive systems*,<sup>\*</sup> systems that must respond to their environment at the environment's speed. When things happen in a reactive system is as important as what happens, making traditional computer programming languages insufficient because they only provide precise control of function. In contrast, my model of computation allows precise synchronization of events by assuming computation is infinitely fast. Familiar to designers of synchronous

<sup>\*</sup> A term due to Harel and Pneuli [34].

digital logic, this divides time into a sequence of discrete "ticks" and allows the designer to control the tick in which an action takes place.

Software is becoming dominant in embedded system design because fast hardware is becoming cheaper. Earlier, custom hardware might have been required because of performance requirements, but now cheap, fast general-purpose microcontrollers are adequate for many of these jobs.

Fast, cheap hardware leads to greater system complexity since it allows larger, more powerful systems to be built. With complexity, however, comes the challenge of designing it correctly. Extensive simulation, and, currently to a lesser extent, formal verification can help in this process, but the easiest way to design a correct system is to design a simple system.

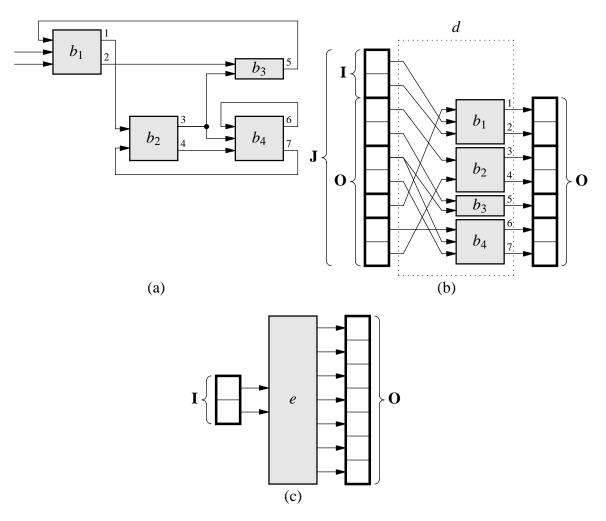

My Synchronous Reactive (SR) model of computation facilitates the design of simple systems because it can combine subsystems described in a variety of languages. For any particular problem, there is usually a language in which it can be solved elegantly. However, the variety of problems in a large system makes no one language ideal, so the need arises for a way to combine different languages. My model supports such heterogeneity by using coarse atomic units of computation: functions that can be as big as entire programs.

I made the SR model deterministic to simplify the design process. It is much more difficult to design and test a system with inherently unpredictable behavior<sup>\*</sup> because both designers and analysis tools need to consider many more possible behaviors.

This model is the first to fuse the idea of instantaneous computation with support for heterogeneous system design. The primary challenge is to maintain the determinacy of such systems in the presence of zero-delay feedback loops. I discuss these problems informally in Section 1.3, and rigorously deal with the problem in Chap-

<sup>\*</sup>This can occasionally be a good thing—nondeterminism is useful for modeling unpredictable environments.

ter 3, where I prove that my model of computation is deterministic.

A reasonable system description language should be defined formally, have a compilation procedure that produces efficient synthesized code (or, equivalently, have a very efficient simulation procedure), and be able to describe practical designs. A formal definition is necessary so that everything that manipulates the design, including the designer, can agree on what a design means. An elegant language that cannot be executed efficiently is not useful by itself, and an elegant language that cannot be used to describe anything useful is similarly useless.

My thesis is that my Synchronous Reactive model of computation is reasonable in this sense. In this dissertation, I present its formal definition and show it is consistent (Chapter 3), present an efficient way to execute it (Chapter 4), and exhibit a practical implementation along with some real examples (Chapter 5). In Chapter 2, I discuss some related system description languages and the final chapter is devoted to conclusions and speculation on future work.

## **1.1 Synchrony**

Using digital circuitry to build logically correct systems has been extremely successful because it allows for abstraction. The idea is simple: using discrete values allows noise below a certain threshold to be filtered out *completely*. The result is an effectively noise-free circuit with behavior that is predictable and reproducible. This allows it to be treated as an ideal mathematical entity.

Synchronous circuits use the same idea to ensure temporal correctness. They discretize time to filter out "time noise" brought on by unpredictable, unmatched, and uncontrollable delays.

Synchronizing an outgoing event with an incoming one is the key ability here. Synchronous digial circuits generally have one synchronizing input: a periodic global clock signal. The synchronous model of time used in SR, which I adopted from the so-called synchronous languages,\* is a generalization of this where every signal from the environment is effectively a clock. All output events are synchronized to the input events; none are produced without outside stimulus.

The ability to synchronize output events to *any* input event allows for great flexibility. In general, it is possible to make something happen on the *n*th occurrence of an event, such as on the tenth second (which requires a periodic "second" input), on the count of three, or on the fifth floor (e.g., for an elevator).

Concurrency is a fundamental requirement for synchrony. Traditional sequential languages such as C are not synchronous because they have no notion of concurrency. For things to be synchronized, they must happen simultaneously, yet a language like C is executed one statement at a time.

The synchronous model of time has a physical interpretation:

**The Synchrony Hypothesis** The system computes infinitely quickly. Each reaction is instantaneous and atomic, dividing time into a sequence of discrete instants. A system's reaction to an input appears at the same instant as the input. (After Berry [5])

A system can behave synchronously if it is fast enough. Specifically, it must always finish its computations before more events arrive. Testing this amounts to testing the synchrony hypothesis, and requires knowing both the minimum inter-event time and the maximum computation time.

The synchronous model of time makes correct systems easier to design and build. It hides temporal details and simplifies the task of synchronizing parts of the system. Activity is easier to specify and understand because the behavior of the system is simplified. Moreover, the technique actually requires less control over the behavior of

<sup>\*</sup>I discuss these in Section 2.3.

a system's components. Their exact speed does not matter provided it is above a certain threshold.

Unfortunately, it is not always practical to build synchronous systems. For example, physically distributed systems with long intrasystem communication times are difficult to make synchronous. But for many applications, especially small embedded ones, synchrony makes sense.

## **1.2 Heterogeneity**

Cheap hardware is enabling designers to create larger systems. These big systems are usually responsible for a wide variety of subtasks, such as a user interface, high-speed digital signal processing, communication, process control, and so forth.

Rarely is a single language ideal for describing each of these subtasks. A C program, for instance, is an excellent way to describe something like a database, but there are better alternatives for describing, say, signal processing. A poor choice of language—one far from the task or the implementation technology—often leads to an inefficient implementation, longer design time, and more design errors.

One approach is a "kitchen sink" language (such as the VHDL language [45], which includes behavioral and structural models), formed by forcibly combining a variety of computational models. Unfortunately, this is limited to using only those models included in the language and generally precludes later expansion. Moreover, analyzing systems described in such a language is harder because of the need to consider many models at once.

A more flexible alternative is to use a language that can coordinate the execution of and communication among subsystems described in a variety of languages. The challenge here is for the coordination language to cope with subsystems it does not understand completely. This approach can be summarized as follows.

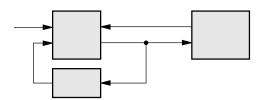

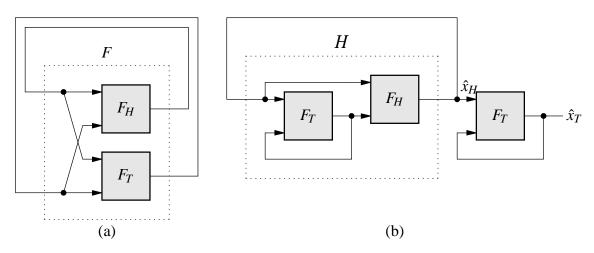

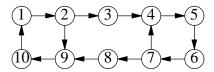

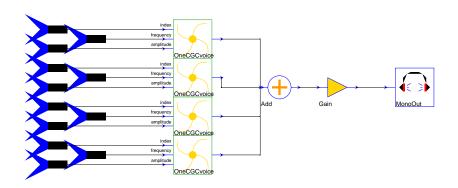

**Figure 1.1** A simple SR system composed of three blocks communicating over three channels. The dangling channel on the left is an input from the environment. Some of the internal channels may be outputs to the environment.

The Black Box Approach to Heterogeneity A system is treated as a set of "black boxes" whose contents may be arbitrary, but whose interfaces conform to a standard. A coordination language controls their execution and all communication between boxes.

When chosen correctly, a black box approach simplifies system analysis because it allows details such as the contents of the boxes to be safely ignored. By contrast analyzing a "kitchen sink" language is harder because the language is complex.

Unfortunately, the black box approach can prohibit the complete analysis of a system. When subsystems are treated too abstractly, certain properties about them cannot be determined. Unfortunately, the heterogeneous approach presented here precludes proving many correctness properties of systems. However, this is not necessarily a drawback because the systems in question are often so large that even if they were specified using a unified scheme, their analysis would be computationally intractable.

## 1.3 SR Systems

An SR system (one described using the SR model of computation) is composed of communicating blocks, as shown in Figure 1.1. The synchrony hypothesis assumes the inputs arrive as a sequence of discrete values and each block's computation is instantaneous. As a result, time in an SR system is a sequence of discrete "ticks," each initi-

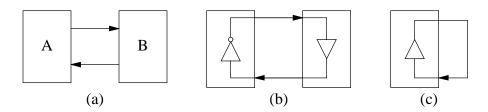

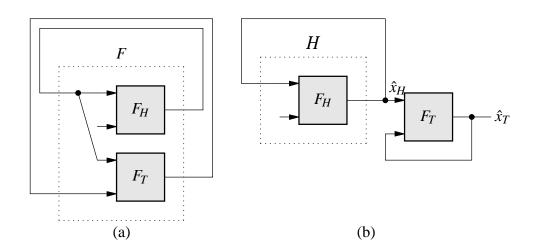

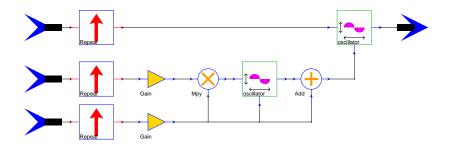

**Figure 1.2** Problems with zero-delay and feedback. (a) Co-dependent: Which should be evaluated first? (b) Paradoxical: Appears to have no solution. (c) Ambiguous: Appears to have many solutions.

ated by the environment. In each tick, each block observes its inputs, instantly computes its outputs (which other blocks see in that same instant), and prepares itself (i.e., changes state) for the next tick.

Blocks communicate among themselves and with the environment through unbuffered unidirectional communication channels. In each tick, each channel takes on exactly one value; there is no buffering. Each channel is driven by either an output of some block or the environment, and may drive any number of block inputs. These connections, along with the number and type of all block inputs and outputs, do not change while the system is running.

#### **1.3.1** Challenges of Zero Delay

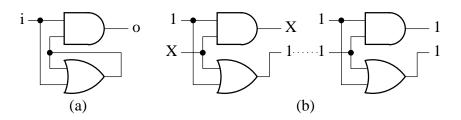

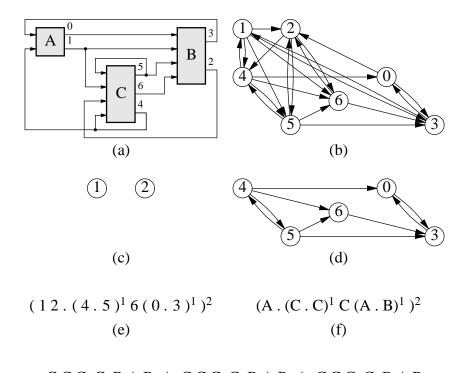

Aside from the single-driver rule, no restrictions are placed on the topology of communication in SR systems. In particular, feedback, including self-loops, is permitted; some synchronous languages disallow them. Maintaining determinism (i.e., for each input there is exactly one reaction) with zero-delay blocks in the presence of feedback is the primary challenge in defining the behavior of these systems. Below, I describe the typical problems that arise in a zero-delay world and how I deal with them.

#### Ordering

To run the software system in Figure 1.2a, one of the blocks needs to be executed first. However, Block A depends on an output from Block B, so it needs to be evaluated later, yet Block B similarly depends on Block A, so which should be evaluated first?

I solve the ordering problem by separating the semantics of SR systems from their implementation. I treat an SR system as equations to be solved rather than as a sequence of functions to evaluate. Thus, it is the responsibility of the scheduler, not the designer, to ensure the blocks in such a system are evaluated in a sensible order. A scheduler based on the results of Chapter 4 might evaluate the blocks in the order ABA, but the designer has no control over this. Instead, the scheduler guarantees an order that produces a predictable result consistent with the formal semantics.

#### Paradoxes

The system in Figure 1.2b is paradoxical. The block on the left wants the two channels to take opposite values, yet the block on the right wants them to be equal, so what values should the channels take?

I solve such paradoxes by making "undefined" one of the possible values for the channels and restricting the class of functions the blocks may compute. The behavior of the system in Figure 1.2b is for both channels to be "undefined." This works because, for the block on the left, the opposite of undefined is undefined (this turns out to be the only reasonable choice), and for the block on the right, undefined is the same as undefined.

#### Nondeterminism

The system in Figure 1.2c appears to be ambiguous. The block only requires that its input and output take the same value, so it appears that the system may have any of a number of possible behaviors.

I deal with such ambiguity by choosing the least-defined solution. For Figure 1.2c, this means the channel will take the undefined value. Restricting the blocks to behave monotonically guarantees the least solution is unique. Moreover, this solution is the only one that does not require assumptions to be made about system behavior, making it more intuitive. The alternative would be a difficult-to-understand "guess-and-test" procedure that would form, test, and refine hypotheses about the values on each channel.

Here, monotonicity means a block will not recant or change its mind about a result. Given a more defined input, it will always produce a consistent output that may be more defined. Fortunately, any function that requires all its inputs to be defined before it produces any outputs is monotonic, making it easy to embed an arbitrary function in an SR system. Many familiar imperative languages (e.g., C, C++, and most assembly languages) implicitly compute such strict functions, so importing blocks from such languages is straightforward.

Chapter 3 is devoted to an extensive, rigorous discussion of the semantics of SR systems, including precise definitions of monotonicity, "undefined," least solutions, and the like.

### 1.3.2 Execution

My execution procedure for SR systems<sup>\*</sup> is based on the idea of relaxation. I calculate the behavior of the system by repeatedly choosing and evaluating blocks until the system has converged to where no block would change the value on any channel. Requiring the blocks to behave monotonically ensures this procedure will always terminate with a unique result. The convergence time is bounded since each channel may become defined at most once in an instant, and there are a fixed, finite number of channels. It can be shown that the

<sup>\*</sup> Others are possible since the semantics in Chapter 3 say nothing about the execution procedure.

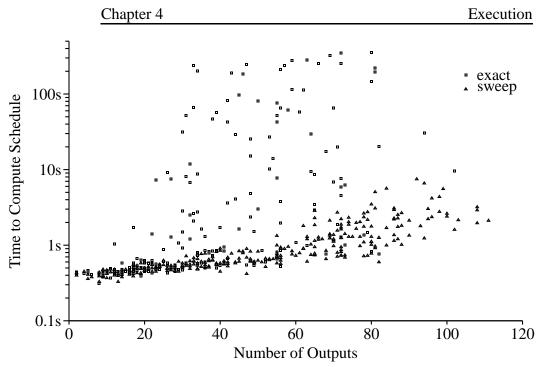

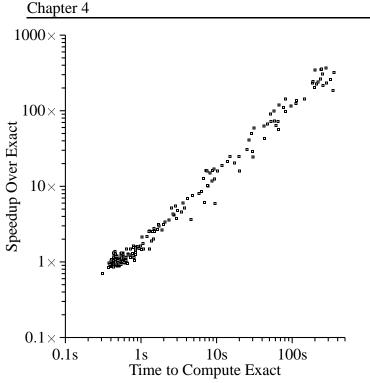

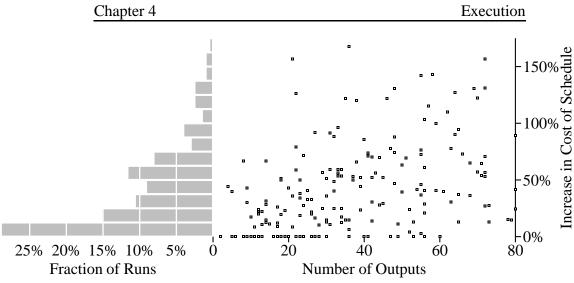

result is the same regardless of which blocks are chosen.

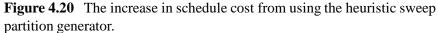

Carefully choosing the block evaluation order makes this execution scheme efficient and predictable. Results in Section 4.3.6 show that in practice the worst-case execution time grows slower than  $n^{1.5}$ , where *n* is the number of block outputs. The challenge is dealing with feedback loops, which I do through a recursive divide-and-conquer strategy that systematically breaks certain feedback loops, iterating them to convergence. Although others have taken the same general approach, mine is the only one that is provably optimum. All of this is discussed in great detail in Chapter 4.

For a block to work within an SR system, it must have an SR interface and be able to compute a monotonic function of its inputs on demand. Beyond that, the "guts" of an SR block can be described and implemented in any way, allowing for heterogeneity. The algorithms in Chapter 4 only needs to know the communication structure of the blocks; not their contents.

A useful side-effect of the heterogeneity of SR systems is their support of truly hierarchical designs. Any group of SR blocks can be encapsulated in a single block without affecting the behavior of the system (although this sometimes affects performance), allowing subsystems to be compiled separately. Currently, all other synchronous languages are "flattened" before they are executed, prohibiting separable compilation and limiting the size and complexity of designs.

## Specification

A specification that will not fit on one page of  $8.5 \times 11$  inch paper cannot be understood. —Mark Ardis

A NY SYNCHRONOUS system with bounded resources behaves like a finite-state machine (FSM), a well-understood and conceptually simple entity, yet in practice such a system is rarely described as an FSM. In this chapter, I discuss why this is and argue the need for a coordination language such as SR to combine subsystems described using application-specific languages. I also discuss some of the languages that inspired SR.

## 2.1 Synchrony and Finite-State Machines

A synchronous system with bounded resources behaves like a finitestate machine. In each instant, the system receives a block of input and produces a block of output based on it. The behavior of such a system is usually time-varying, meaning the output in an instant is a function of both the input in that particular instant and the *history* of the system—the inputs in all earlier instants. The history of the system can be thought of as its *state*—an internal configuration that affects the output function and changes from instant to instant. Bounded memory resources can only distinguish a finite number of these histories, hence the machine has a finite number of states. A synchronous finite-state machine consists of is six things:\*

$$(Q, \Sigma, \Delta, \delta, \lambda, q_0)$$

where

- Q is the finite set of states

- $\Sigma$  is the finite input alphabet: a set of symbols

- $\Delta$  is the finite output alphabet: a set of symbols

- $\delta$  is the transition function mapping  $Q \times \Sigma$  to Q

- $\lambda$  is the output function<sup>†</sup> mapping  $Q \times \Sigma$  to  $\Delta$

- $q_0$  is the initial state (in Q)

When a state machine is in state q and input a arrives, it produces output  $\lambda(q, a) \in \Delta$  and goes to state  $\delta(q, a) \in Q$ . It starts in state  $q_0$ .

This is the complete story for *every* synchronous system. In theory, only these six things need to be described; in practice, each can easily become unmanageably complex.

Describing the input and output alphabets is often the easiest task. Sometimes they are small enough to be listed directly, or they may be a simple subset of a familiar set such as the integers. More often, they are sets of vectors described using a complex data type from a programming language such as C or Pascal.

In contrast, describing the state set, the transition function, and the output function is difficult because of the sheer size of the domains involved. A vector-valued input alphabet grows exponentially with the width of its vectors, so even small vectors can render an enumeration-based description of the output or transition functions

<sup>\*</sup>This notation is taken from Hopcroft and Ullman [35], a standard reference on the subject of automata theory.

<sup>&</sup>lt;sup>†</sup>Note that for reactivity, the output depends on both the state and the input.

impractical. Clearly, a useful specification scheme must allow a designer to succinctly specify exponentially large sections of these. In general, this is the problem of succinctness.

## 2.2 Succinctness

Succinct description is a goal of all languages. It is generally easier to make a short description correct because there are fewer places to make mistakes. Similarly, analyzing a succinct description is usually easier because solving a small problem is usually easier than solving a large one.

An ideal design language would allow succinct descriptions of *all* designs, but this is theoretically impossible because there are simply too many possible designs. Real languages try instead to make the description of some reasonable subset of designs succinct; other systems have either a verbose description or none at all.

This fundamental barrier is partly responsible for the enormous number of design languages that have been developed. Designers and design tools alike crave succinct descriptions, so many application areas have had special-purpose languages designed for them.

As systems grow larger and more diverse, however, it becomes less likely that a single language will be able to succinctly describe all parts of a given system. Although for each subsystem, there will be a language that can describe it succinctly, no one language will be the best for all subsystems.

One solution to this problem is the ability to connect and coordinate heterogeneously-specified subsystems. In this way, existing work on specification languages can be leveraged to provide more powerful ways to specify systems. This is the heterogeneous philosophy behind SR.

In this thesis, I concentrate on one way of combining subsystems (i.e., concurrently) that appears to be a very natural way for designers to think. It can be found in virtually all higher-level languages for deThe system has two inputs, *reset* and *next*, and three outputs, *a*, *b*, and *c*. Whenever *reset* appears, *a* is emitted. After this, the first *next* signal produces a *b*, and the second *next* signal produces a *c*.

**Figure 2.1** The sequencer example, a simple reactive system, described in English.

scribing reactive systems (e.g., those presented in the next section), and is often the hardest aspect of these languages to design correctly because of the sometimes paradoxical implications of zero delay.

## 2.3 Synchronous Languages

In this section, I present a collection of synchronous languages\* that illustrate some of the issues that arise in specifying synchronous systems. All rely on the synchrony hypothesis, and all are capable of specifying arbitrary finite-state machines, yet for a particular design, one is usually better than the others. To contrast the languages and illustrate this point, I have implemented a simple reactive system in each language, described in Figure 2.1 and hereafter called the sequencer example.

The description in Figure 2.1 is deliberately vague to illustrate a point. Especially in synchronous designs, it is easy to overlook a particular case, yet the system must handle all cases. When *next* and *reset* appear together, what should happen? The description suggests *a* is emitted, but what about the other outputs? I have chosen to make *a* take precedence, but other choices are possible. The right one usually depends on the system's environment.

The languages I present in this section range from the obvious to the subtle. The most obvious lists the output and next-state functions

<sup>\*</sup>Halbwachs's book [32] and a special issue of Proceedings of the IEEE [3] provide a more comprehensive summary of these.

in a table. Traditional state diagrams are essentially these tables with a graphical syntax and input predicates. Derived from these are the textual OC format, which introduces more sophisticated predicates and actions, and the graphical Argos, which just adds hierarchy and concurrency. The imperative language Esterel departs completely from an explicit list of states. Lustre is an even greater departure, concentrating almost exclusively on arithmetic and having very little notion of state.

Each language needs some procedure for checking the validity of a description. The difficulty of this varies with the language and the level of validity to be verified, but in general the more succinct the descriptions, the harder it is. This is unfortunate, but is a natural sideeffect of languages that allow a succinct description of complex behavior.

### 2.3.1 Tabular Form

The most obvious way to describe a synchronous finite-state machine is to list the output and next state functions for each possible input and present state, e.g., Figure 2.2. Even such a small system illustrates the problem with this approach—the number of rows in the table grows exponentially with the number of inputs.

Checking that a table is consistent is simple: there must be exactly one row for each state/input combination, and each output and next state must be an allowed output or state.

### 2.3.2 State Diagrams

State diagrams (e.g., Figure 2.3) are a slight improvement over tables. These are graphs where each node represents a state. Each arc is labeled with an input that causes a transition from one state to another and the output produced when this happens. The labels take the form "input predicate/outputs." The input predicate is a conjunction of true and complemented signals, and the outputs are simply a list of

| reset | next | PS | NS | a | b | c |

|-------|------|----|----|---|---|---|

| 0     | 0    | Α  | Α  | 0 | 0 | 0 |

| 0     | 1    | Α  | А  | 0 | 0 | 0 |

| 1     | 0    | Α  | В  | 1 | 0 | 0 |

| 1     | 1    | Α  | В  | 1 | 0 | 0 |

| 0     | 0    | В  | В  | 0 | 0 | 0 |

| 0     | 1    | В  | С  | 0 | 1 | 0 |

| 1     | 0    | В  | В  | 1 | 0 | 0 |

| 1     | 1    | В  | В  | 1 | 0 | 0 |

| 0     | 0    | С  | C  | 0 | 0 | 0 |

| 0     | 1    | С  | А  | 0 | 0 | 1 |

| 1     | 0    | С  | А  | 1 | 0 | 0 |

| 1     | 1    | С  | А  | 1 | 0 | 0 |

**Figure 2.2** The sequencer example described with a table. Inputs are on the left; outputs are on the right. PS is "present state;" NS is "Next State."

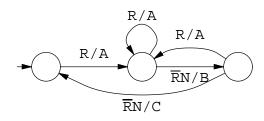

Figure 2.3 The sequencer example described using a state diagram

signals to emit. By convention, if no arc from the current state has a true predicate, the machine stays in that state and emits nothing. The initial state is marked with a short arrow leading to it.

State diagrams are usually preferable to tables, since the multidimensional nature of the transitions are more easily visualized, but they are not much more compact. The only advantage comes when the predicates are simple relative to the number of cases, or when most actions are "do nothing."

Using predicates instead of an explicit representation makes consistency checking more difficult. A state diagram is nondeterministic if there are ever two arcs from a single state with simultaneously true predicates, something that requires knowing all possible inputs.

#### **2.3.3 The OC Format**

The OC ("Object Code") format [68] (see also Caspi et al. [19]) was developed as a common intermediate language for the synchronous languages Esterel, Lustre, and Argos. Of the synchronous languages I present in this section, OC code is the easiest to execute on a sequential processor. It is well-suited to describing sequential control processes, but does not have any of the concurrency or preemption of some higher-level languages.

An OC program describes a single finite-state machine. Each state has an attached decision tree whose nodes are indices into an action table and whose leaves are pointers to next states. The action table is a list of atomic behaviors that include testing a signal or variable, emitting a signal, computing the new value of a variable, or calling an external function.

Figure 2.4 depicts the sequencer example described in a stylized OC format. For such a simple example, it is comparatively verbose, but it allows much more complex predicates and actions, including arithmetic.

Representing concurrent behavior with an OC program is difficult

| Action Table: |               |               |

|---------------|---------------|---------------|

| 0: if R then  |               |               |

| 1: if N then  |               |               |

| 2: emit A     |               |               |

| 3: emit B     |               |               |

| 4: emit C     |               |               |

|               |               |               |

| State 0:      | State 1:      | State 2:      |

| (0) if R then | (0) if R then | (0) if R then |

| (2) emit A    | (2) emit A    | (2) emit A    |

| goto 1        | goto 1        | goto 1        |

| goto O        | (1) if N then | (1) if N then |

|               | (3) emit B    | (4) emit C    |

|               | goto 2        | goto O        |

|               | goto 1        | goto 2        |

Figure 2.4 The sequencer example described in OC

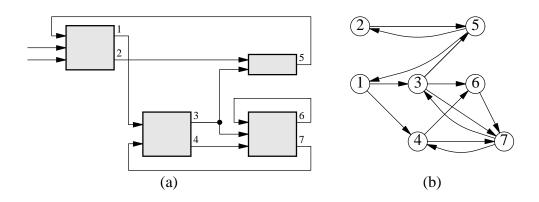

because it only describes a single FSM. For example, in the Esterel program of Figure 2.5a, it is fairly easy to see that signal B only depends on signal A, yet if the program is compiled into OC, B may also appear to depend on C in the resulting program (Figure 2.5b), incorrectly causing the system in Figure 2.6a to deadlock. There are other ways to compile this program, but all suffer from this problem of artificial dependencies. The problem, fundamentally, is that OC forces two events that could happen simultaneously to happen in a particular order.

### 2.3.4 Argos

Maraninchi's hierarchical finite-state machine language Argos [48, 49, 30] is a purely synchronous derivative of Harel's informal but influential Statecharts [33]. Later attempts to formalize the Statecharts semantics [56, 36] were somewhat successful, but the confusion has

```

Actions:

0: if C then

1: if A then

2: emit B

module TWOWIRES:

3: emit D

input A, C;

output B, D;

State 0:

every A do emit B end

(0) if C then

(3)

emit D

(1)

if A then

every C do emit D end

end module

(2)

emit B

goto 0

(1)

if A then

(2)

emit B

goto O

(a)

(b)

```

**Figure 2.5** (a) A simple Esterel program. (b) Its OC representation. Parentheses surround action numbers.

**Figure 2.6** The problem with flattening concurrency. If the order in which the module processes its inputs is fixed, one of these systems will incorrectly deadlock.

Figure 2.7 The sequencer example described in Argos

resulted in some twenty-two variants of the language [72], of which Argos is perhaps the cleanest.

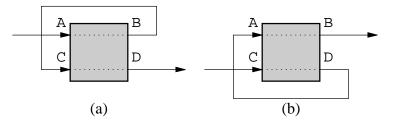

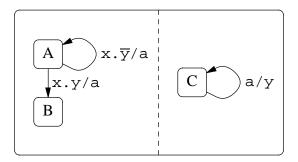

An Argos specification is a hierarchical state diagram. When a state encloses one or more states, there are two possibilities. If the inner states are "OR" states (e.g., those in State B in Figure 2.7), exactly one of the inner states is active when the enclosing state is active; if the inner states are "AND" states (drawn with dashed lines separating them, as in Figure 2.8), *all* of the inner states will be active.

Figure 2.7 shows an Argos implementation of the sequencer example. It starts in State A and waits for the r signal. When r is present, the system emits the a signal and enters States B and C, since State C is the initial state (denoted by its sourceless arrow) in the collection of OR-states in State B.

The Argos semantics require the ability to partially evaluate input predicates. Figure 2.8 illustrates this. When the signal x is present, neither  $x \cdot \overline{y}$  nor  $x \cdot y$  holds since the status of y has not been established, but a is emitted anyway since it is the action in both cases. This allows the self-loop on State C to fire, emitting y, and causing the arc to State B to fire completely.

Checking an Argos program for consistency is more difficult than checking a state diagram. Again, determinism requires that no more than one arc from a state have a true predicate. This requires at least some boolean analysis, but a more precise check might take into ac-

**Figure 2.8** Incremental behavior in an Argos program. When in State A, x arriving causes a and y to be emitted and the system to enter State B.

```

module RESTART:

input RESET, NEXT;

output A, B, C;

every RESET do

emit A ;

await NEXT ; emit B ;

await NEXT ; emit C

end

end module

```

count which states (actually, combinations of states) of the system can be reached through some sequence of inputs. Solving this problem for large systems is currently at the frontier of formal verification research.

### 2.3.5 Esterel

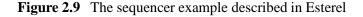

Berry's synchronous language Esterel [7, 4] is textual, imperative, and well-suited for specifying sequential control-dominated tasks. It is concurrent and deterministic, and supports preemption and exceptions. An Esterel program is a group of concurrently-executing modChapter 2

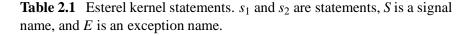

| Statement                         | Meaning                                                           |

|-----------------------------------|-------------------------------------------------------------------|

| nothing                           | Do nothing.                                                       |

| pause                             | Pause until the next instant.                                     |

| signal $S$ in $s_1$ end           | Introduce local signal $S$ and execute $s_1$ .                    |

| emit S                            | Make S present in this instant.                                   |

| $s_1 i s_2$                       | Execute $s_1$ . When it terminates, execute $s_2$ .               |

| $ s_1    s_2$                     | Execute $s_1$ and $s_2$ until both terminate.                     |

| loop $s_1$ end                    | Execute $s_1$ and restart it when it terminates.                  |

| present $S$ then $s_1$ else $s_2$ | If <i>S</i> is present, execute $s_1$ , otherwise execute $s_2$ . |

| suspend $s_1$ when $S$            | Execute $s_1$ in the current instant and in later in-             |

|                                   | stants where S is absent.                                         |

| trap $E$ in $s_1$ end             | Introduce the local exception $E$ and execute $s_1$ .             |

| exit E                            | Terminate the enclosing trap <i>E</i> statement.                  |

ules that communicate through signals that in each instant are either absent or present with a value.

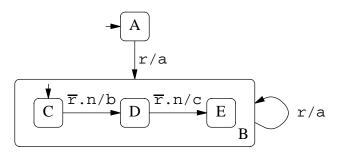

Figure 2.9 shows Esterel can be very succinct in specifying sequential behavior. Essentially, a three-state machine that emits A, B, and C is enclosed by a loop that restarts it whenever reset appears.

The language consists of a set of kernel statements from which other, more complex control structures are built. This kernel,<sup>\*</sup> which deals only with pure (non-valued) signals, is shown in Table 2.1. For example, the derived statement await S, which terminates in the next instant in which S is present, can be built from kernel statements as follows:

<sup>\*</sup>The kernel has continued to evolve since its first incarnation. The kernel presented here is from Berry's book [6].

```

trap T in

loop

pause ;

present S then exit T end

end

end

```

The full Esterel language also has simple arithmetic operations and variables along with a host of higher-level control constructs built from kernel statements.

Reincarnation is an odd aspect of the Esterel language. In certain cases, such as the one below, a signal may appear to take two or more values in a single instant.

```

loop

signal S in

present S then emit O else nothing end ;

pause ;

emit S

end signal

end loop

```

In the second instant, the signal S is emitted, the signal statement terminates, and the loop resets with a fresh, absent copy of the S signal. Signal O is not emitted. Detecting these cases and correctly expanding them into a format like OC has been a challenge for those writing compilers for the language.

Checking the consistency of an Esterel program is more difficult than any of the other languages presented here. It is easy to write paradoxes (see Section 1.3.1) in the language, and exactly checking for them involves exploring every possible execution of the program. The latest compiler (V4, as of this writing) does this symbolically after converting the program to a circuit. See Section 3.1.2 and Shiple et al. [64] for more details.

| Constants            | true 0 -5 5.3e-2 |

|----------------------|------------------|

|                      |                  |

| Variables            | a x is_set       |

| Arithmetic operators | + - * / div mod  |

| Boolean operators    | and or not       |

| Relational operators | = < <= > >=      |

| Conditional          | if then else     |

| Delay                | pre              |

| Initialization       | ->               |

| Downsampling         | when             |

| Upsampling           | current          |

**Table 2.2** Components of Lustre flow expressions.

#### 2.3.6 Lustre

Caspi et al.'s Lustre language [20, 31] is a declarative, textual synchronous language with a dataflow flavor. A Lustre program consists mainly of expressions that define *flows*—a possibly infinite sequence of values of a particular type along with a clock, a sequence of times for the sequence of values. All of these expressions are running concurrently and are order-independent.

Lustre flow expressions are built from the components shown in Table 2.2. Operators work pointwise on flows with identical clocks, a compiler-enforced restriction. For example, if x and y are flows with values  $(x_1, x_2, ...)$  and  $(y_1, y_2, ...)$  and identical clocks, then  $x+y = (x_1 + y_1, x_2 + y_2, ...)$ .

Delay and initialization operators add sequential behavior to the language. The pre operator adds memory—it delays a flow by one clock cycle. Specifically, pre  $\mathbf{x} = (nil, x_1, x_2, ...)$  (*nil* denotes undefined). The -> ("followed by") operator makes it possible to initialize memory by changing the first value of a flow. Specifically,  $\mathbf{x} \rightarrow \mathbf{y} = (x_1, y_2, y_3, ...)$ .

| С            | 0     | 1     | 0                     | 1                     | 0                     | 0     | 1                     | 0                     |

|--------------|-------|-------|-----------------------|-----------------------|-----------------------|-------|-----------------------|-----------------------|

| Х            | $x_1$ | $x_2$ | <i>x</i> <sub>3</sub> | <i>x</i> <sub>4</sub> | <i>x</i> <sub>5</sub> | $x_6$ | <i>x</i> <sub>7</sub> | <i>x</i> <sub>8</sub> |

| Y = X when C |       | $x_2$ |                       | $x_4$                 |                       |       | <i>x</i> <sub>7</sub> |                       |

| current Y    | nil   | $x_2$ | $x_2$                 | $x_4$                 | $x_4$                 | $x_4$ | <i>x</i> <sub>7</sub> | <i>x</i> <sub>7</sub> |

Figure 2.10 The relationship between the when and current operators.

```

node RESTART(reset, next: bool)

returns (a, b, c: bool);

var clock: bool;

let

clock = reset or next;

(a, b, c) =

current( COUNTABC(reset when clock) )

and clock;

tel.

node COUNTABC(reset: bool)

return a, b, c: bool;

let

a = reset;

b = (false -> pre(a)) and not reset;

c = (false \rightarrow pre(b)) and not reset;

tel.

```

Figure 2.11 The sequencer example described in Lustre

Two sampling operators impose a tree structure to the clocks in a Lustre program. The downsampling when operator creates a flow whose clock is defined by a boolean flow; the upsampling current operator interpolates a flow so that its clock is the one on the boolean flow that generated the clock. Figure 2.10 illustrates the relationship between these two operators. The compiler uses a simple syntactic unification algorithm to tell when clocks on signals are identical.

Figure 2.11 shows the sequencer example written in Lustre. The specification is clumsy because the example is sequential—Lustre is better-suited to specifying multirate dataflow systems.

Consistency checking is fairly easy for Lustre. Feedback loops

without a pre operator are prohibited, something easily checked. The other challenge is checking clock consistency, which amounts to verifying the clocks on the signals feeding to an operator are the same.

## 2.4 Heterogeneous Languages

In this section, I review two languages supporting heterogeneity that inspired my own. Unlike SR, both are targeted toward data-centric applications, but they illustrate the heterogeneous approach to system specification.

In Kahn's programming language, the restrictions on the interface and contents of the blocks ensure determinacy. Further restrictions give Lee's Synchronous Data Flow, which trades some of the flexibility of Kahn's scheme for nearly complete compile-time analysis, including memory usage, termination, and run-time behavior.

#### 2.4.1 Kahn Process Networks

Kahn, in an early influential paper [38], presented a simple language for parallel programming based on a process model. It defines a system as a set of parallel-executing processes that communicate exclusively through single-input, single-output FIFOs. When a process reads a data token from one of these FIFOs, it blocks until one is available. Kahn showed that this restriction was sufficient to make these systems determinate, rendering the sequence of data tokens on each FIFO independent of process execution order or speed.

Figure 2.12 shows a simple process in Kahn's language that acts as a switch. Integers on input U are alternately sent through outputs V and W. As its name suggests, the wait statement waits for the next value to arrive on an input.

Executing these networks without doing unnecessary work or using more memory than needed is challenging. Compile-time analysis is impossible in general, since each process can be described in a

```

Chapter 2

```

```

Process g(integer in U; integer out V, W);

Begin integer I; logical B;

B := true;

Repeat Begin

I := wait(U);

if B then send I on V else send I on W;

B := not B;

End;

End;

```

Figure 2.12 A process in Kahn's language.

Turing-complete language. Kahn and MacQueen [39] discussed this problem in a later paper, and Parks [54] solves the problem with a scheduling scheme that runs one of these networks in bounded memory and time if possible.

### 2.4.2 Synchronous Data Flow

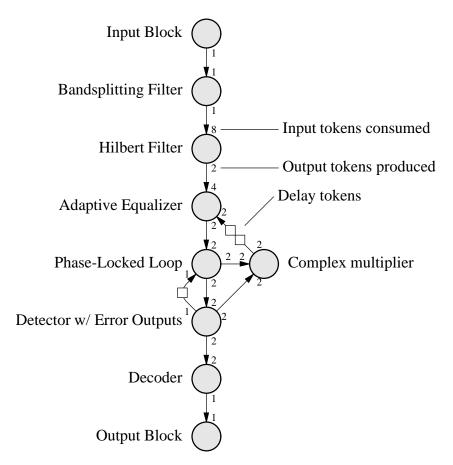

Lee and Messerschmitt's Synchronous Data Flow (SDF) [43, 42] is another block diagram language that takes a heterogeneous approach. It is well-suited for describing multirate digital signal processing systems and can be compiled to produce very efficient, predictable code. Figure 2.13 shows a typical SDF application—a modem.

SDF is a subclass of the class of dataflow process network languages,\* which are themselves a subclass of the Kahn process network languages. SDF gives up Turing-completeness in return for extensive compile-time predictability. In particular, it can be scheduled statically, removing all run-time scheduling decisions and allowing memory consumption to be predicted exactly.

An SDF system is composed of a collection of blocks that communicate through single-driver, single-receiver FIFO buffers. The exe-

<sup>\*</sup> see Lee and Parks [44] for a good summary of these

cution of a block is divided into atomic "firings" where the block consumes and produces a fixed number of tokens on each FIFO. In executing the system, all blocks are fired in a sequence that periodically returns the number of tokens on each buffer to its initial value. In this way, the system can run forever without over- or under-flowing any communication buffer.

Knowing such a sequence of block firings at compile time leads to a simple compilation technique known as block code generation. In it, the code for each block's firing is concatenated together according to the firing sequence. The advantage of this is that the code for each block firing can be optimized by hand—a boon for programmable DSPs, whose code is often difficult to optimize automatically.

An SDF system is deterministic because it is a Kahn process network. The sequence of tokens that appear on each FIFO is guaranteed to be the same for any valid execution of the system.

One problem with SDF is that it is not compositional. Coalescing two blocks into one can cause deadlock where none would exist in the original system. This does not always happen, and there are heuristics for avoiding it (see Bhattacharyya et al.'s work on scheduling SDF graphs [8]), but it cannot be avoided in general. It is disturbing, however, that something as simple as two wires cannot be modeled as an SDF block. This diminishes the heterogeneous nature of SDF, implying there is a class of subsystems whose behavior cannot be encapsulated. Furthermore, designs cannot be truly hierarchical; all hierarchy must be flattened completely to avoid introducing artifical deadlock.

SR avoids SDF's compositionality problem by effectively allowing partial or incremental firing of blocks. It is SDF's inability to do this that prevents it from modeling a wire. SDF's firing rules impose more synchronization at block boundaries than is present in the rest of the system. Since SR systems are completely synchronous, this problem does not arise.

Figure 2.13 An SDF description of a modem, adapted from Lee [41].

| Scheme  | Blocks                  | Communication          | Concurrency              |

|---------|-------------------------|------------------------|--------------------------|

| SR      | Monotonic functions     | Single-driver,         | Each block computes a    |

|         | selected by a state     | multiple-receiver      | function in each instant |

|         | machine                 | channels, one value    | and advances its state   |

|         |                         | per instant            |                          |

| Argos   | Hierarchically-nested   | Broadcast signals      | Each FSM produces        |

|         | finite-state machines   | present or absent in   | output and advances its  |

|         |                         | each instant           | state each instant       |

| Esterel | Sequential and parallel | Broadcast signals      | In each instant, each    |

|         | imperative statements   | present or absent in   | block runs until it is   |

|         |                         | each instant           | waiting for the next     |

| _       |                         |                        | instant                  |

| Lustre  | Arithmetic & boolean    | Broadcast flows:       | Each operator            |

|         | operators, delays,      | sequences of data with | computes once each       |

|         | down- and up-samplers   | an associated clock    | instant                  |

| Kahn    | Sequential imperative   | Unbounded              | Each process runs        |

|         | statements              | unidirectional FIFOs   | unless blocked by a      |

|         |                         | with blocking reads    | read from an empty       |

|         |                         |                        | FIFO                     |

| SDF     | Produce and consume     | Unidirectional FIFOs;  | Processes fire in a      |

|         | a fixed number of       | size computable at     | repeating sequence       |

|         | tokens each firing      | compile time           |                          |

Table 2.3

A comparison of some system specification schemes

# Semantics

The test of a first-rate intelligence is the ability to hold two opposed ideas in the mind at the same time, and still retain the ability to function. —F. Scott Fitzgerald

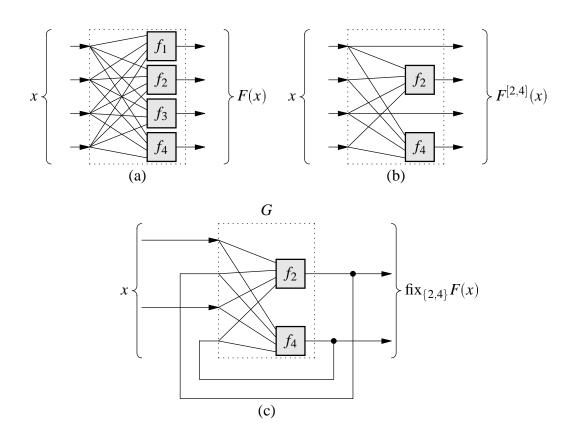

N THIS CHAPTER, I formally define the semantics of the SR model of computation. The main problem is unambiguously interpreting systems with zero-delay feedback loops, which I do by treating the blocks of a system as a system of equations. I use a well-known theorem from discrete mathematics to show the system has exactly one solution. To my knowledge, these are the first formal semantics for heterogeneous synchronous systems.

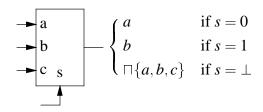

The meaning of an SR system in an instant is the least solution of f(x) = x, where x is the values in the communication channels and f is the function computed by the blocks for a particular set of inputs. By restricting the blocks' behavior to be monotonic and making certain values of x more defined than others, there is always a unique least x for any input, making SR systems deterministic.

I take a fixed point approach because both the programming language semantics community and the digital circuit simulation community use it to give meaning to recursive or self-referential entities. As such, it is both mathematically sound and physically realistic.

The semantics I present say nothing about how to execute these systems. This was deliberate—by not addressing the problem, it be-

comes easier to devise new ways to execute these systems. For example, a scheduler for simulation might minimize average execution time, whereas a scheduler for implementation might minimize worstcase execution time. Any approach whose result adheres to the semantics is acceptable.

This chapter contains three sections. In the first, I further motivate the fixed-point approach by reviewing the approaches two communities have taken to similar problems. In the second, I review the discrete mathematics of complete partial orders and continuous functions, which I use in the third section to define the semantics of SR Systems, ultimately showing they are unambiguous and thus deterministic.

# 3.1 Motivation

It is surprising that both the programming language semantics and the digital circuit simulation community arrived at nearly the same solution to assigning meaning to recursive or self-referential entities. After all, the simulation community had to choose something that matched physical reality, whereas the semantics community was free to choose any mathematically sound approach. Despite these differences, the solution is roughly the same, suggesting it is somehow natural.

In the remainder of this section, I present the solution to this problem from each community's viewpoint. The core ideas form the basis for the formal semantics I present in Section 3.3.

### **3.1.1 Denotational Semantics**

In the denotational approach to programming language semantics, pioneered by Dana Scott and Christopher Strachey [62, 61, 65] in the early 1970s, the meaning of a program fragment is defined by mapping it to an element, often a function, in a semantic domain. For example, the recursively-defined factorial function in Figure 3.1a might

|                              | ÷                |

|------------------------------|------------------|

|                              | $f(-2) = \perp$  |

| <pre>int fact(int x) {</pre> | $f(-1) ~=~ \bot$ |

| if ( $x == 0$ ) return 1;    | f(0) = 1         |

| else return x * fact(x-1);   | f(1) = 1         |

| }                            | f(2) = 2         |

|                              | f(3) = 6         |

|                              | f(4) = 24        |

|                              | :                |

| (a)                          | (b)              |

**Figure 3.1** (a) A recursive definition of the factorial function. (b) The denotational meaning of this function.  $\perp$  denotes non-termination.

be mapped to the function f in Figure 3.1b. The idea is to abstract away details of a program, such as the names of variables or the algorithm and concentrate purely on the effects of the fragment.

A denotational way of looking at a function definition is as a fixedpoint equation. For example, the recursive definition of the fact function in Figure 3.1a can be thought of as an equation,

$$f(x) = \begin{cases} 1 & \text{if } x = 0\\ x \cdot f(x-1) & \text{otherwise,} \end{cases}$$

(3.1)

and the meaning of the recursive function definition is a function f that satisfies (3.1). More abstractly, a recursive function definition is a function F that transforms a function to a function. In this way, (3.1) can be written more simply as

$$f = \mathbf{F}(f). \tag{3.2}$$

An obvious question to ask is whether (3.2) has a solution and, if so, is it unique? It turns out that when f is a member of a com-

plete partial order, a particular form of ordered set discussed in Section 3.2.1, and the function F is continuous, a concept discussed in Section 3.2.2, (3.2) always has a unique least solution, making this a reasonable way to interpret a function definition.

Zero-delay feedback looks like recursion, so I use this approach to handling recursive definitions to define SR systems with feedback. In my case, f is a vector-valued function defining the values on the communication channels, and F corresponds to evaluating all of the blocks in parallel. I present the details in Section 3.3.

Kahn's formal semantics for his concurrent dataflow language [38] (see Section 2.4.1) also use the fixed-point approach. He interprets each process as a function defined on potentially infinite streams of data, which represent the contents of the FIFOs his processes use to communicate. The semantics of a system with feedback is the solution to a fixed point equation defined on these streams.

Kahn's fixed point considers the whole execution history of the system. The values on the streams form a complete partial order—a set whose elements have a notion of "definedness"—under a prefix ordering. E.g., the stream 01 is less defined than the stream 01101. Under this prefix ordering, any process that waits when reading from an empty FIFO computes a continuous function, meaning that when more input is presented to a process, it may not change or reduce the amount of data it has already produced, nor may it wait forever. By requiring all processes to use such blocking reads, Kahn's systems are provably deterministic.

There is much more to denotational semantics. See the books by Winskel [73], Gunter [29], Stoy [65], Schmidt [60], and Allison [1].

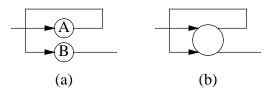

#### 3.1.2 Circuit Simulation

Circuit simulation has traditionally proceeded along two paths. Analog simulation attempts to model virtually all circuits, whereas digital or switch-level simulation treats only a restricted class of circuits

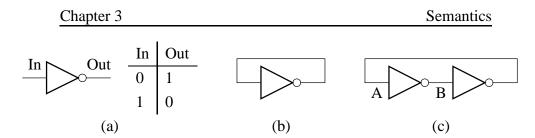

**Figure 3.2** (a) An ideal binary inverter and its truth table. (b) A feedback circuit with no stable states. (c) A feedback circuit with two stable states.

in exchange for simulation speed. Progress along each path has often come from borrowing ideas from the other. Simpler models and the use of digital approximations has expedited analog simulation; more realistic models and other analog simulation techniques have improved digital simulation accuracy.

Analog simulation techniques are based on models from applied physics and use continuous mathematics. Pederson [55] provides an excellent historical review. A circuit is typically modeled as a system of ordinary non-linear differential equations and solved by a numerical integration method such the Trapezoidal Rule or a Runge-Kutta method. Newton's method is used on the resulting nonlinear systems, and LU decomposition or a sparse linear system solver is applied to the resulting linear systems.

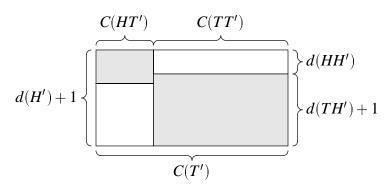

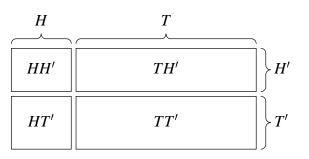

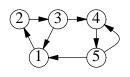

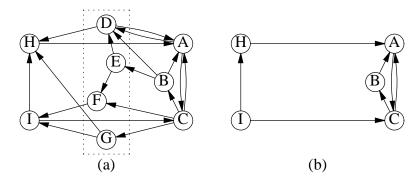

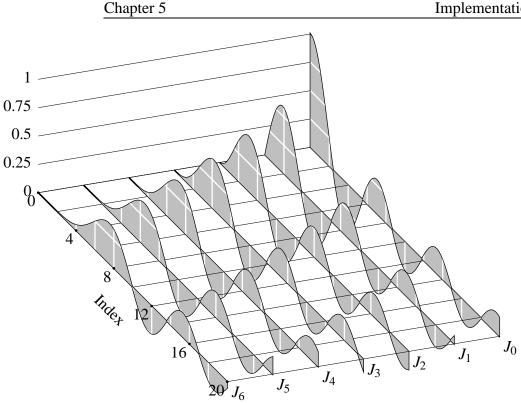

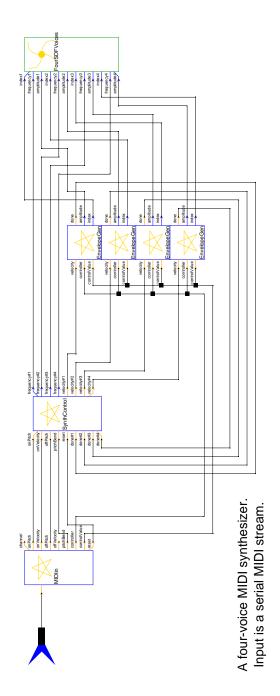

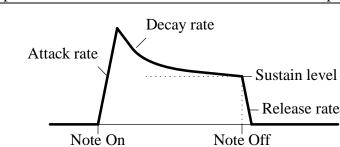

By contrast, digital circuit simulators work with circuits that look very much like my SR systems: ideal (zero-delay) gates with an associated discrete function and well-defined inputs and outputs. Simulation consists of evaluating each gate (computing its outputs as a function of its inputs) in a topological order starting at the inputs to the circuit. Circuits with feedback, however, present a problem because their gates have no topological order.