**1999 Ptolemy Miniconference**

# **Control Logic using Finite State Machines**

# **Bilung Lee**

Edward A. Lee

Department of EECS, UC Berkeley February 19, 1999 Major collaborator: Xiaojun Liu

p. 1 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY

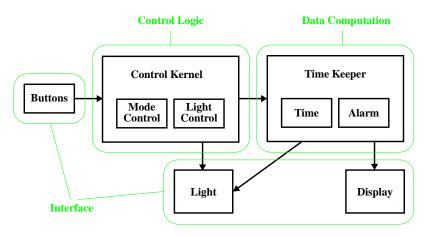

# Problem

• Modern systems tend to include nontrivial control logic

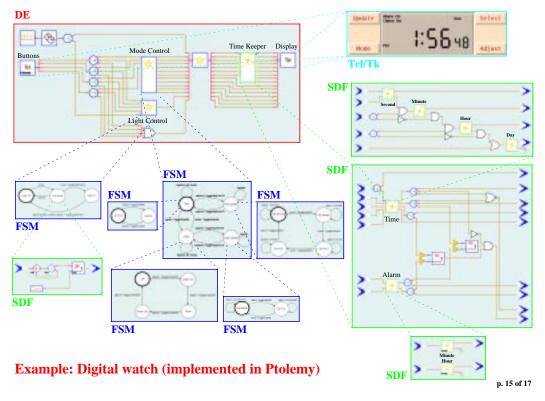

**Example: Digital watch**

How to describe such a system?

p. 2 of 17

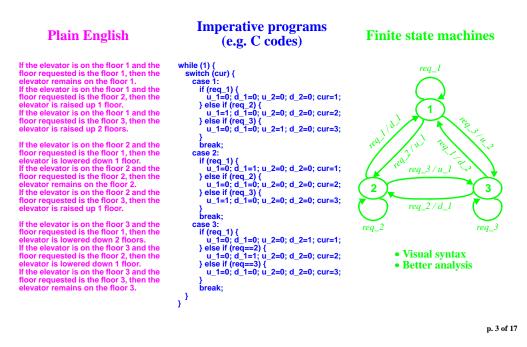

# How to Describe the Control Logic?

#### • Example: Elevator controller

UNIVERSITY OF CALIFORNIA AT BERKELEY

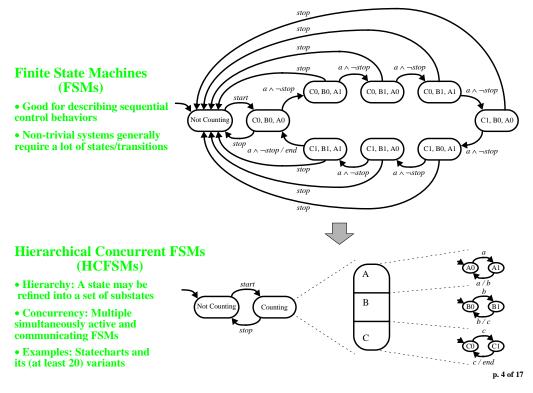

# **Upgrade to Hierarchical Concurrent FSMs**

UNIVERSITY OF CALIFORNIA AT BERKELEY

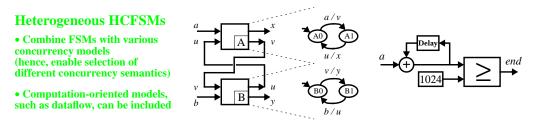

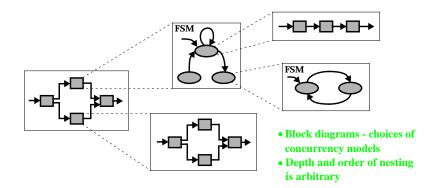

# **Upgrade to Heterogeneous HCFSMs**

#### **HCFSMs**

• Good for describing complex control behaviors

• Most models tightly integrate only one concurrency semantics, for example, Argos = SR + FSM and CFSM = DE + FSM

• Not suitable for specifying computation-oriented tasks (hence, hard to specify a complete design)

p. 5 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY

# **Design Methodology**

**Objective:** A system specification scheme capable to

- Describe both control logic and computation tasks

- Specify composite behaviors (concurrency and hierarchy)

- Enable the selection of different concurrency semantics

(No existing schemes support all of the above three)

**Heterogeneous approach:**

- Allow hierarchy and heterogeneity in the FSM

- Let the FSM be hierarchically combined with other existing concurrency models

- Choose the most appropriate model for the problem at hand

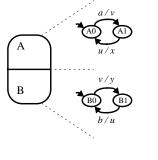

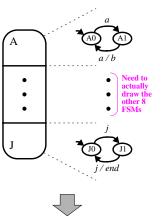

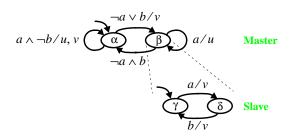

# **Hierarchy in FSMs**

• A state of an FSM may be refined into another FSM

- Inputs/outputs of the slave are a subset of those of its master

- The slave reacts first, and then its master reacts

- Strength

- Reduce the number of transitions

p. 7 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY

# **Heterogeneity in FSMs**

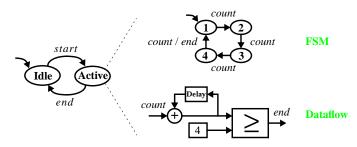

• The slave inside a state of the FSM need not be an FSM

- Key Principle

- The slave must have a well-defined determinate and finite operation, called a *step* of the slave

- The slave is invoked first, and then its master reacts

- Strength

- Appropriate models can be included for different situations (e.g. dataflow for computation-intensive tasks)

# Heterogeneity in FSMs (continued)

- FSMs may be used inside modules of other model

#### • Key Principle

- The model must provide a way to determine the inputs for each module and when the module should react

- These FSMs are concurrent FSMs when the model contains concurrency semantics

- Strengths

- Concurrency is naturally included

- Reduce the number of states

p. 9 of 17

#### UNIVERSITY OF CALIFORNIA AT BERKELEY

# Mixing FSMs with Concurrency Models

#### • Strength

• Heterogeneity, hierarchy, concurrency and FSMs are all included

## • Current focus: Interaction of FSMs with

- Synchronous Dataflow (SDF)

- Discrete Events (DE)

- Synchronous/Reactive Model (SR)

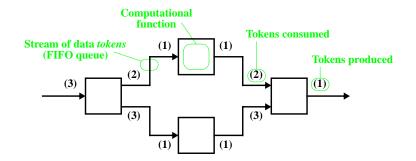

# **Synchronous Dataflow (SDF)**

#### To interact with the FSM

- Event encoding

- Absent/Present event in FSM  $\leftrightarrow$  0/1 valued token in SDF

- FSM inside SDF

- One block firing in SDF  $\rightarrow$  One reaction of FSM

- SDF inside FSM

- One slave step in FSM  $\rightarrow$  One iteration of SDF

p. 11 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY

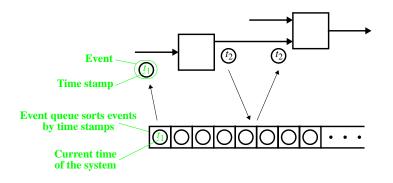

# **Discrete Events (DE)**

#### To interact with the FSM

- Events passed through FSM have the same time stamps

- FSM inside DE

- One block firing in  $DE \rightarrow One reaction of FSM$

- DE inside FSM

- One slave step in FSM  $\rightarrow$  Simulation of DE up to time stamp of input

# Synchronous/Reactive Model (SR)

- To interact with the FSM

- Support  $\perp$  in the FSM

| absent present |     | $\land 0 1 \perp$         | $\vee$ | 0      | 1      | $\perp$ |

|----------------|-----|---------------------------|--------|--------|--------|---------|

|                | 0 1 | 0 0 0 0                   | 0      | 0      | 1      | $\perp$ |

| $\sim$         | 1 0 | $1 0 1 \perp$             | 1      | 1      | 1      | $\bot$  |

| $\perp$        |     | $\perp$ 0 $\perp$ $\perp$ | $\bot$ | $\bot$ | $\bot$ | $\perp$ |

- FSM inside SR

- + One block firing in  $SR \rightarrow One \ reaction \ of \ FSM$

- SR inside FSM

- One slave step in FSM  $\rightarrow$  One instant of SR

p. 13 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY

# **Characteristics of Different Models**

| Model<br>(one step)                                                     | Strengths                                                                                                                                                      | Weaknesses                                                                                   |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Finite State<br>Machines<br>(one reaction)                              | <ul> <li>Good for sequential control</li> <li>Can be made deterministic (often is not, however)</li> <li>Map well to hardware and software</li> </ul>          | • Computation-intensive<br>systems are hard to specify                                       |

| Synchronous<br>Dataflow<br>(one iteration)                              | <ul> <li>Good for signal processing</li> <li>Loosely synchronized</li> <li>Deterministic</li> <li>Map well to hardware and software</li> </ul>                 | • Control-intensive systems<br>are hard to specify                                           |

| Discrete Events<br>(simulation up to<br>the time stamp of<br>the input) | <ul> <li>Good for asynchronous digital hard-<br/>ware</li> <li>Globally synchronized</li> <li>Can be made deterministic (often is<br/>not, however)</li> </ul> | <ul> <li>Expensive to implement<br/>in software</li> <li>May over-specify systems</li> </ul> |

| Synchronous/<br>Reactive Model<br>(one instant)                         | <ul> <li>Good for control-intensive systems</li> <li>Tightly synchronized</li> <li>Deterministic</li> <li>Map well to hardware and software</li> </ul>         | • Computation-intensive<br>system are over-specified                                         |

# **Capability for a Complete Design**

UNIVERSITY OF CALIFORNIA AT BERKELEY

# State<br/>TransitionsImperative<br/>ConstructsHierarchy<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>Concurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>Concurrency<br/>for<br/>Concurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>Concurrency<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>TransitionsChoic<br/>for<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>TransitionsChoic<br/>for<br/>for<br/>State<br/>TransitionsConcurrency<br/>for<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>State<br/>

**Comparison with Related Work**

| Specification<br>Schemes | State<br>Transitions | Imperative<br>Constructs | for<br>State<br>Transitions | for<br>State<br>Transitions | for<br>Imperative<br>Constructs | Choices<br>of<br>Concurrency |

|--------------------------|----------------------|--------------------------|-----------------------------|-----------------------------|---------------------------------|------------------------------|

| SDL                      |                      | 0                        | 0                           |                             | 0                               | 0                            |

| Statecharts              |                      | 0                        |                             |                             | 0                               | 0                            |

| Argos                    |                      | 0                        |                             |                             | 0                               | 0                            |

| CFSM                     |                      | 0                        |                             |                             | 0                               | 0                            |

| Mini-<br>Statecharts     | •                    | 0                        | •                           | •                           | 0                               | ⊛                            |

| Argos +<br>Lustre        | •                    | •                        | •                           | •                           |                                 | 0                            |

| SpecCharts               |                      |                          |                             |                             |                                 | 0                            |

| Stateflow +<br>Simulink  | •                    | •                        | •                           | •                           |                                 | *                            |

| This work                |                      |                          |                             |                             |                                 |                              |

| • : Fully sup            | oported. 🛞 : I       | Partially supp           | orted. 🔿 : N                | ot supported.               | 1                               | 1                            |

# Conclusions

## • Heterogeneous combination

- FSMs can be hierarchically combined with multiple concurrency models

- Different models have strengths and weaknesses, and thus are best suitable in certain situations

- Although only three concurrency models are discussed, the combination can be extended for other models, e.g. CSP, CT, etc., as long as we provide their interaction mechanisms

#### • Design framework

- Subsystems can be separately specified and designed

- The simple and determinate mechanisms we provide can be used to combine the subsystems as a whole for validation using simulation

- Example: Digital cellular phone

Team 1: SDF + FSM for modem, speech coder Team 2: SR + FSM for user interface controller

Team 3: DE + FSM for communication protocol

Team 4: Combine results for validation

p. 17 of 17

UNIVERSITY OF CALIFORNIA AT BERKELEY