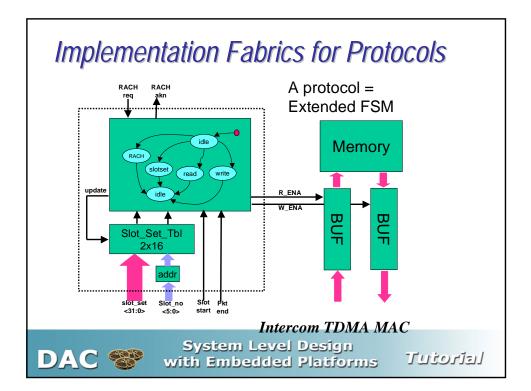

|                              | m TDMA I<br>nentation a                                                                                   | MAC<br>Internatives            | 6             |

|------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------|---------------|

|                              | ASIC                                                                                                      | FPGA                           | AR M8         |

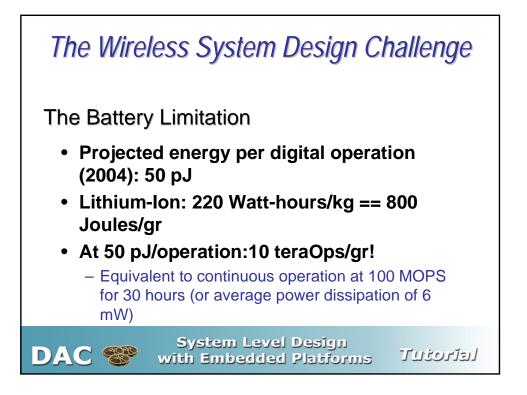

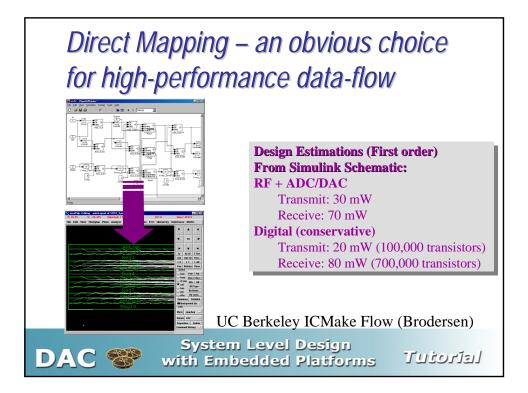

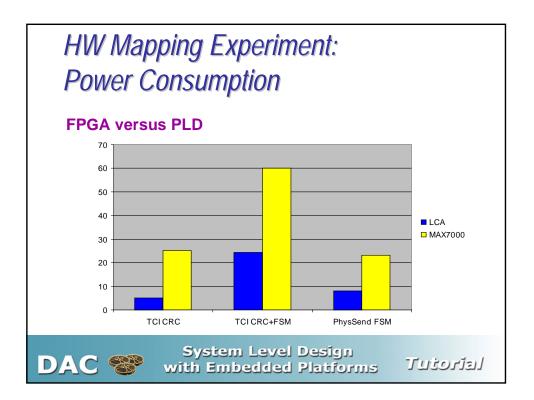

| Power                        | 0.26mW                                                                                                    | 2.1mW                          | 114mW         |

| Energy                       | 10.2pJ/op                                                                                                 | 81.4pJ/op                      | n*457pJ/op    |

| FPGA: 1<br>ARM8:<br>Ratio: 1 | V, 0.25 μm CMOS pro<br>1.5 V 0.25 μm CMOS<br>1 V 25 MHz processor<br>- 8 - >> 400<br>2 <b>much flexib</b> | low-energy FPGA                | needed?       |

| DAC 🐔                        | Systen                                                                                                    | n Level Desig<br>bedded Platfo | n et la de la |

## Summary

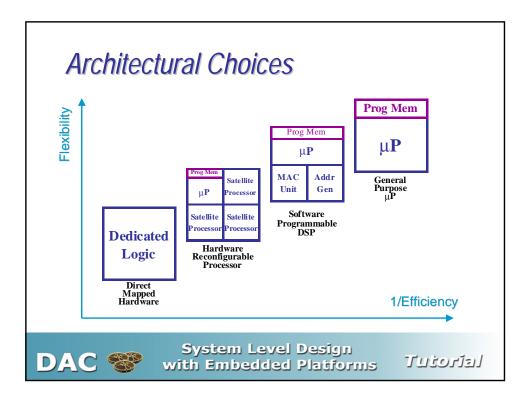

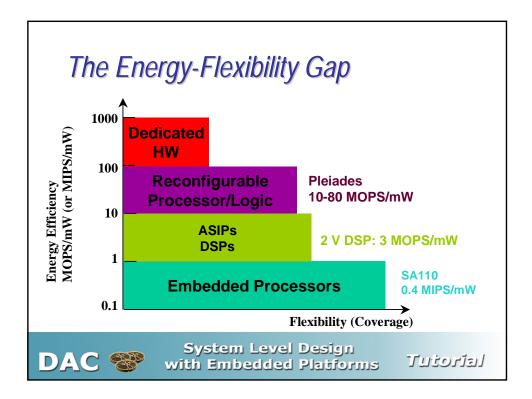

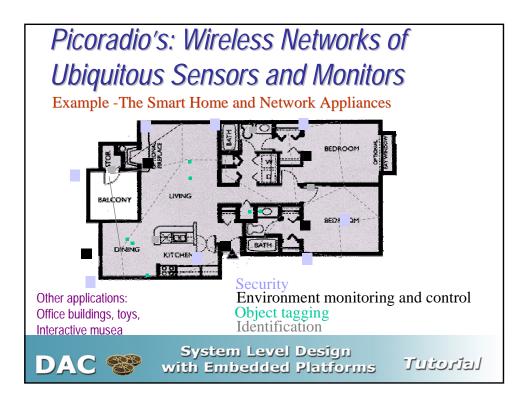

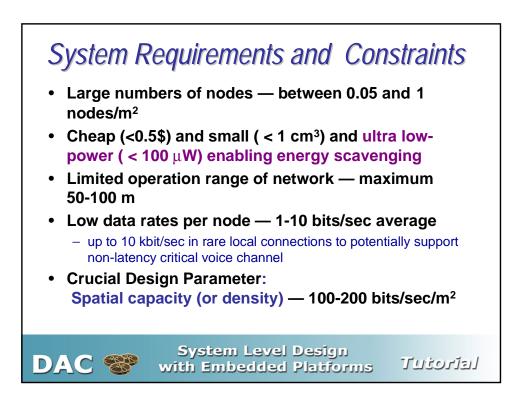

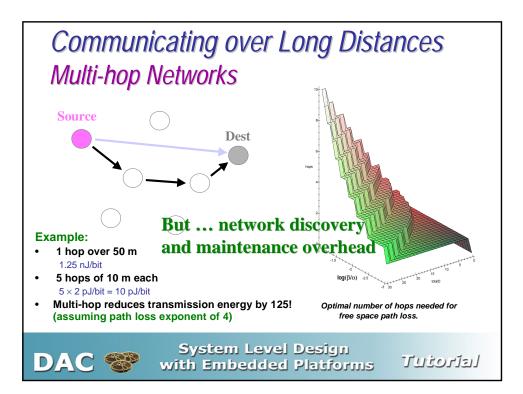

- Low-energy design ascends to prime time forced mainly by the last-meter problem

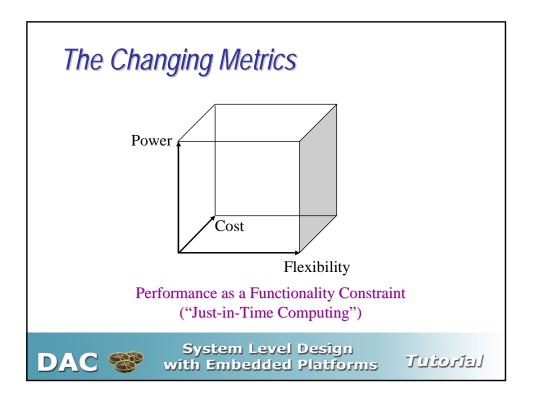

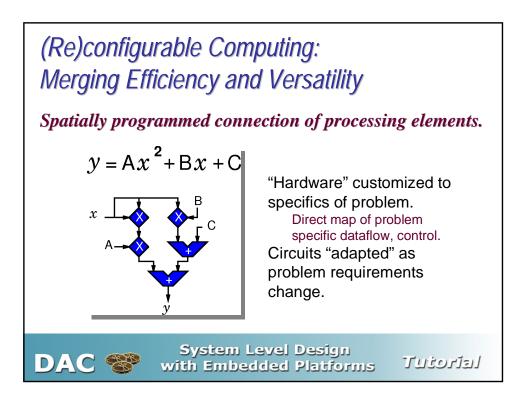

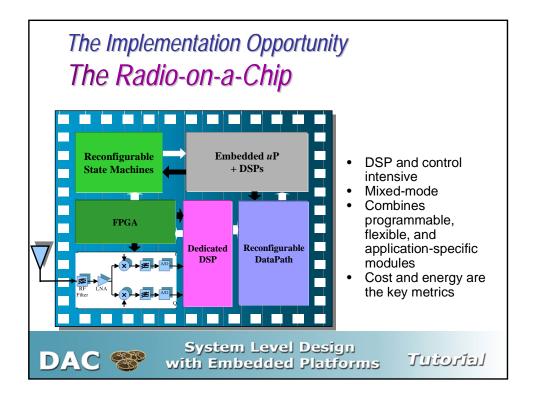

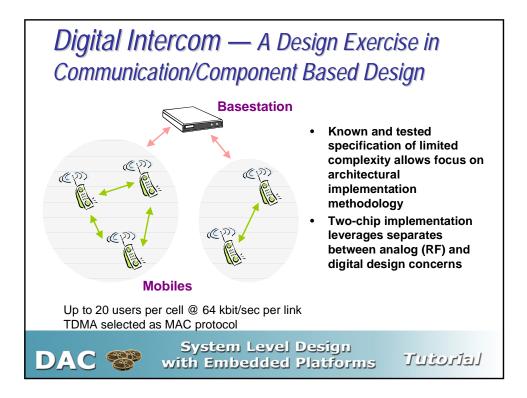

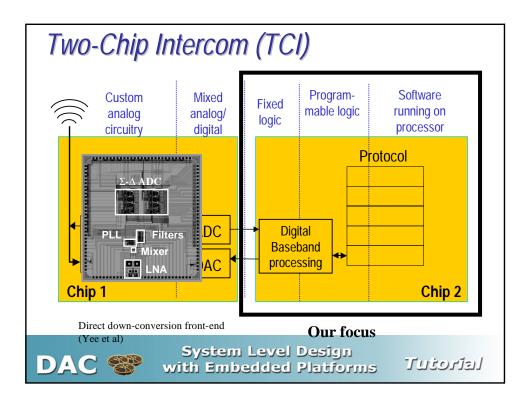

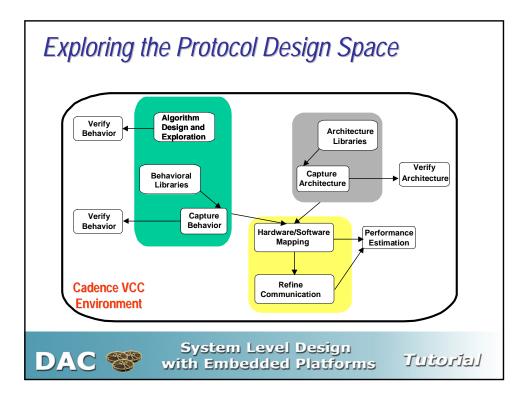

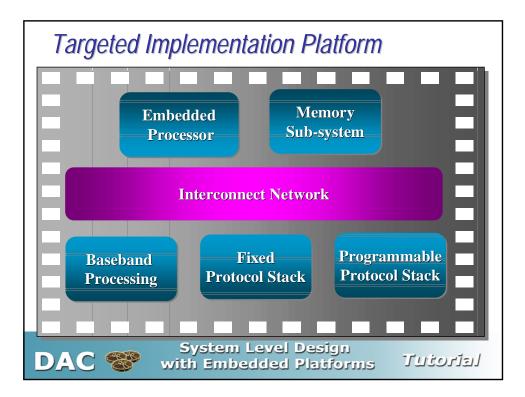

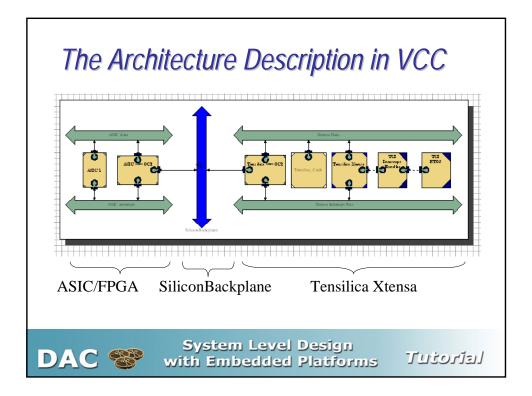

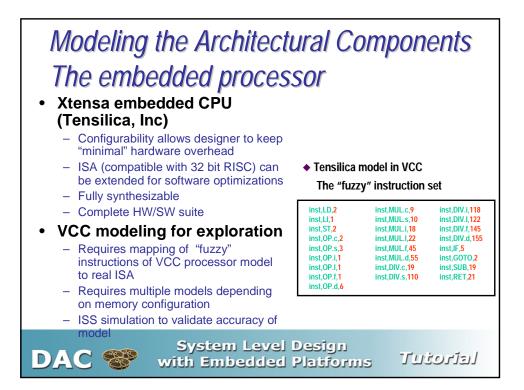

- System-on-a-Chip approach enables and demands heterogeneous implementation strategies, sometimes involving non-intuitive and innovative design platforms

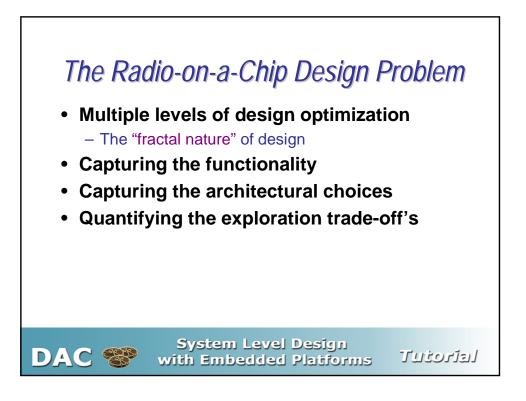

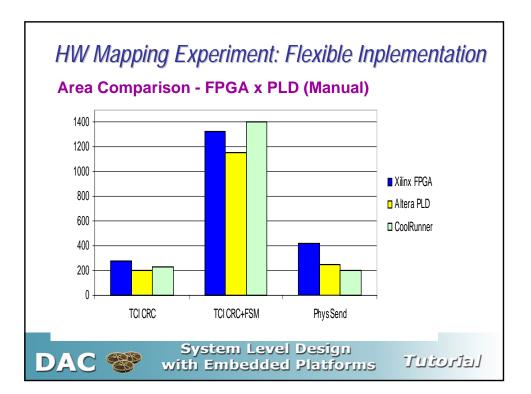

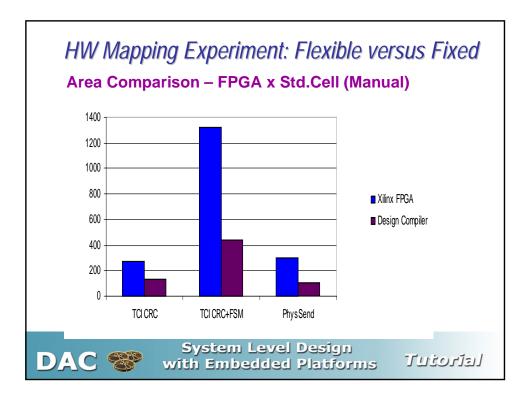

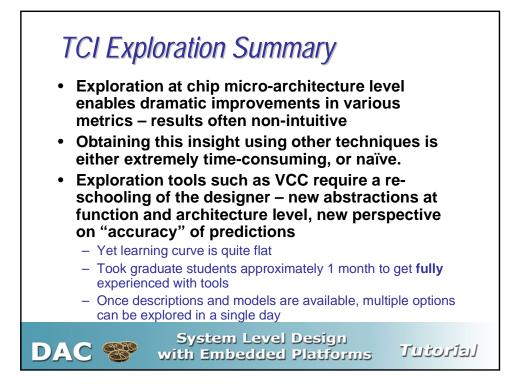

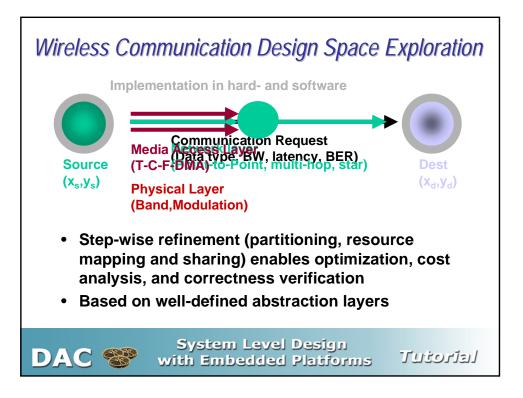

- Design exploration over various fabrics and partitions has dramatic impact on dominant metrics, such as energy and cost

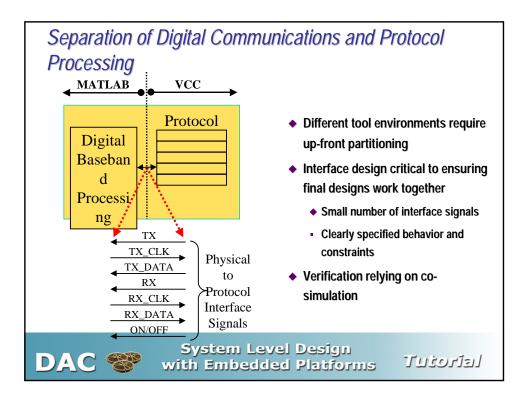

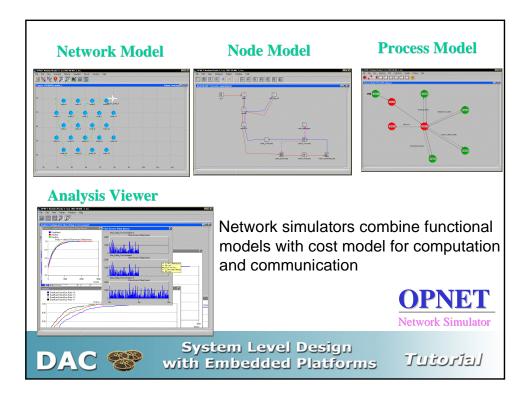

- It requires orthogonalization of function and architecture, supplemented with performance models (cost, time, energy)

Architectural models for exploration in high demand

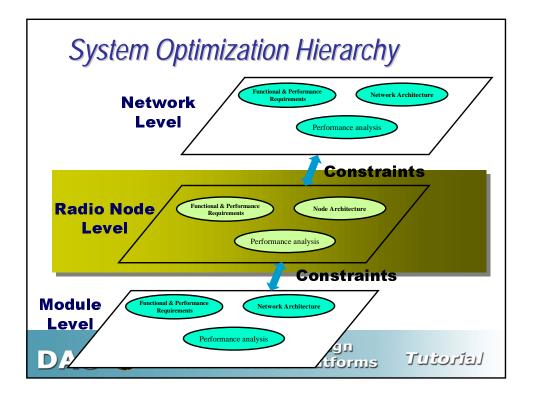

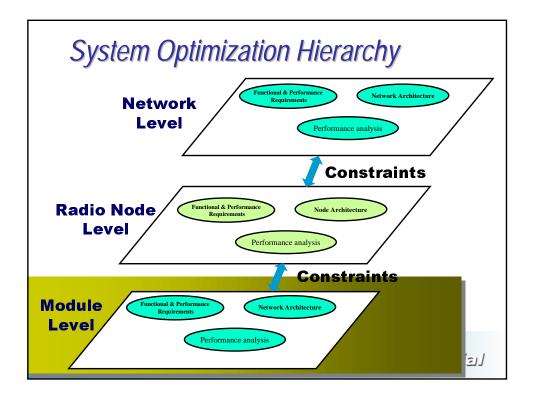

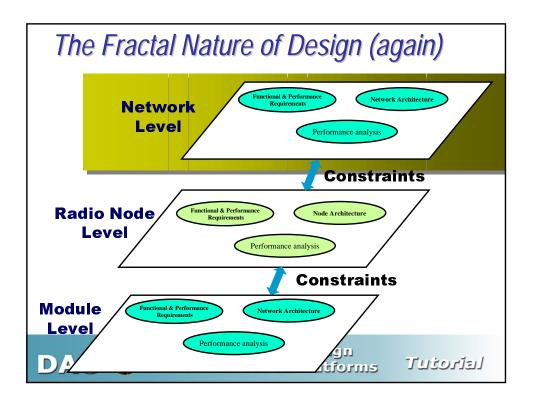

- This methodology holds at all levels of the system hierarchy The Fractal Nature of Design

System Level Design with Embedded Platforms

Tuiorial