Design Space Exploration of Stream-based Dataflow Architectures *Methods and Tools*

A.C.J. Kienhuis

## Design Space Exploration of Stream-based Dataflow Architectures

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.F. Wakker, in het openbaar te verdedigen ten overstaan van een commissie, door het College voor Promoties aangewezen, op vrijdag 29 Januari 1999 te 10:30 uur

door

Albert Carl Jan KIENHUIS

elektrotechnisch ingenieur geboren te Vleuten.

Dit proefschrift is goedgekeurd door de promotor: Prof.dr.ir. P.M. Dewilde

Toegevoegd promotor: Dr.ir. E.F. Deprettere.

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter Prof.dr.ir. P.M. Dewilde, Dr.ir. E.F. Deprettere, Ir. K.A. Vissers, Prof.dr.ir. J.L. van Meerbergen, Prof.Dr.-Ing. R. Ernst, Prof.dr. S. Vassiliadis, Prof.dr.ir. R.H.J.M. Otten,

Technische Universiteit Delft, promotor Technische Universiteit Delft, toegevoegd promotor Philips Research Eindhoven Technische Universiteit Eindhoven Technische Universiteit Braunschweig Technische Universiteit Delft Technische Universiteit Delft

Ir. K.A. Vissers en Dr.ir. P. van der Wolf van Philips Research Eindhoven, hebben als begeleiders in belangrijke mate aan de totstandkoming van het proefschrift bijgedragen.

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Kienhuis, Albert Carl Jan

Design Space Exploration of Stream-based Dataflow Architectures : Methods and Tools Albert Carl Jan Kienhuis. -Delft: Delft University of Technology Thesis Technische Universiteit Delft. - With index, ref. - With summary in Dutch ISBN 90-5326-029-3 Subject headings: IC-design; Data flow Computing; Systems Analysis

Copyright © 1999 by A.C.J. Kienhuis, Amsterdam, The Netherlands. All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in the Netherlands

# Contents

| 1 | Intro                | oduction 1                                                   |  |  |  |  |  |  |

|---|----------------------|--------------------------------------------------------------|--|--|--|--|--|--|

|   | 1.1                  | Motivation                                                   |  |  |  |  |  |  |

|   | 1.2                  | Video Signal Processing in a TV-set                          |  |  |  |  |  |  |

|   |                      | 1.2.1 TV-set                                                 |  |  |  |  |  |  |

|   |                      | 1.2.2 Video Processing Architectures in the TV of the Future |  |  |  |  |  |  |

|   |                      | 1.2.3 Stream-Based Dataflow Architecture                     |  |  |  |  |  |  |

|   | 1.3                  | Design Space Exploration                                     |  |  |  |  |  |  |

|   | 1.4                  | Main Contributions of Thesis                                 |  |  |  |  |  |  |

|   | 1.5                  | Outline of the Thesis 11                                     |  |  |  |  |  |  |

| 2 | Basi                 | c Definitions and Problem Statement 15                       |  |  |  |  |  |  |

|   | 2.1                  | Stream-based Dataflow Architectures                          |  |  |  |  |  |  |

|   |                      | 2.1.1 Definitions                                            |  |  |  |  |  |  |

|   |                      | 2.1.2 Structure                                              |  |  |  |  |  |  |

|   |                      | 2.1.3 Behavior                                               |  |  |  |  |  |  |

|   | 2.2                  | The Class of Stream-based Dataflow Architectures             |  |  |  |  |  |  |

|   |                      | 2.2.1 Architecture Template                                  |  |  |  |  |  |  |

|   |                      | 2.2.2 Design Space                                           |  |  |  |  |  |  |

|   | 2.3                  | The Designer's Problem                                       |  |  |  |  |  |  |

|   |                      | 2.3.1 Exploring the Design Space of Architectures            |  |  |  |  |  |  |

|   |                      | 2.3.2 Problems in Current Design Approaches                  |  |  |  |  |  |  |

|   | 2.4                  | Related Work on Dataflow Architectures                       |  |  |  |  |  |  |

|   |                      | 2.4.1 Implementation Problems of Dataflow Architectures      |  |  |  |  |  |  |

|   |                      | 2.4.2 Other Dataflow Architectures                           |  |  |  |  |  |  |

|   |                      | 2.4.3 Implementing Stream-based Dataflow Architectures       |  |  |  |  |  |  |

|   | 2.5                  | Conclusions                                                  |  |  |  |  |  |  |

| 3 | Solution Approach 43 |                                                              |  |  |  |  |  |  |

|   | 3.1                  | The Evaluation of Alternative Architectures                  |  |  |  |  |  |  |

|   |                      | 3.1.1 Quantitative Data                                      |  |  |  |  |  |  |

|   |                      | 3.1.2 The Y-chart Approach                                   |  |  |  |  |  |  |

|   | 3.2                  | Design Space Exploration Using the Y-chart Approach          |  |  |  |  |  |  |

|   | 3.3                  | Requirements of the Y-chart Approach                         |  |  |  |  |  |  |

|   |                      | 3.3.1 Performance Analysis                                   |  |  |  |  |  |  |

|   |                      | 3.3.2 Mapping                                                |  |  |  |  |  |  |

|   | 3.4                  | Development of a Y-chart Environment                         |  |  |  |  |  |  |

|   | 3.5  | Related Work                                                                                    |  |  |  |  |  |  |  |

|---|------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|   |      | 3.5.1 Design of General-Purpose Processors                                                      |  |  |  |  |  |  |  |

|   |      | 3.5.2 Design of Application-Specific Architectures                                              |  |  |  |  |  |  |  |

|   | 3.6  | Conclusions                                                                                     |  |  |  |  |  |  |  |

| 4 | Porf | ormance Analysis 63                                                                             |  |  |  |  |  |  |  |

| 4 |      | Performance Analysis                                                                            |  |  |  |  |  |  |  |

|   | 4.1  | 4.1.1 A System                                                                                  |  |  |  |  |  |  |  |

|   |      | 4.1.2 Performance Modeling                                                                      |  |  |  |  |  |  |  |

|   |      | 4.1.2       Performance Evaluation       65         4.1.3       Performance Evaluation       65 |  |  |  |  |  |  |  |

|   |      |                                                                                                 |  |  |  |  |  |  |  |

|   |      | 5                                                                                               |  |  |  |  |  |  |  |

|   | 4.2  | 4.1.5       Trade-off       66         The PAMELA Method       66                               |  |  |  |  |  |  |  |

|   | 4.2  |                                                                                                 |  |  |  |  |  |  |  |

|   |      | · · · · · · · · · · · · · · · · · · ·                                                           |  |  |  |  |  |  |  |

|   |      |                                                                                                 |  |  |  |  |  |  |  |

|   | 1 2  | 1                                                                                               |  |  |  |  |  |  |  |

|   | 4.3  | Objectives in Using the PAMELA Method                                                           |  |  |  |  |  |  |  |

|   | 4.4  | An Object Oriented Modeling Approach using PAMELA                                               |  |  |  |  |  |  |  |

|   |      | 4.4.1 The Object                                                                                |  |  |  |  |  |  |  |

|   |      | 4.4.2 Modeling a System as a Network of Objects                                                 |  |  |  |  |  |  |  |

|   |      | 4.4.3 Describing the Structure of an Object in C++                                              |  |  |  |  |  |  |  |

|   |      | 4.4.4 Describing the Behavior of an Object Using PAMELA                                         |  |  |  |  |  |  |  |

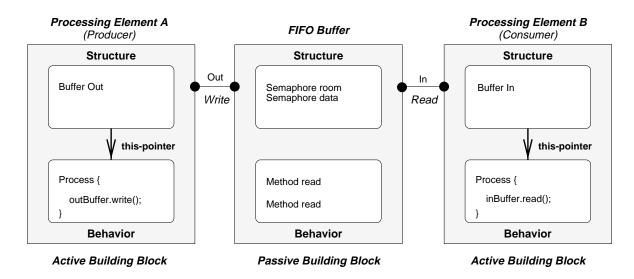

|   |      | 4.4.5 Building Blocks                                                                           |  |  |  |  |  |  |  |

|   | 4.5  | Simulating Performance Models with the RTL                                                      |  |  |  |  |  |  |  |

|   | 4.6  | Related Work                                                                                    |  |  |  |  |  |  |  |

|   | 4.7  | Conclusions                                                                                     |  |  |  |  |  |  |  |

| 5 | Arch | Architectures 91                                                                                |  |  |  |  |  |  |  |

|   | 5.1  | Architectures                                                                                   |  |  |  |  |  |  |  |

|   |      | 5.1.1 Pictorial Representation                                                                  |  |  |  |  |  |  |  |

|   |      | 5.1.2 Architectures                                                                             |  |  |  |  |  |  |  |

|   |      | 5.1.3 Cycle-accurate Model                                                                      |  |  |  |  |  |  |  |

|   | 5.2  | Modeling Architectures                                                                          |  |  |  |  |  |  |  |

|   | 5.3  | Modeling Architectures using the PMB                                                            |  |  |  |  |  |  |  |

|   |      | 5.3.1 Machine-oriented Modeling Approach                                                        |  |  |  |  |  |  |  |

|   |      | 5.3.2 Building Blocks                                                                           |  |  |  |  |  |  |  |

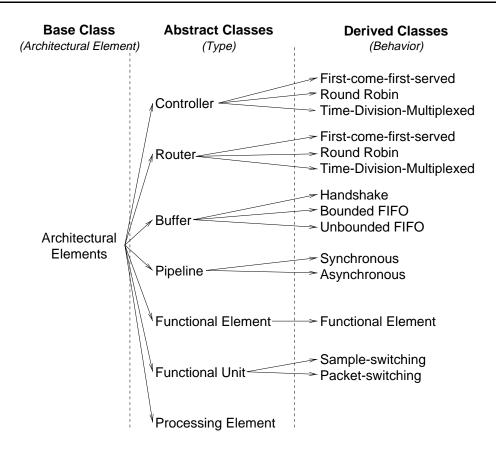

|   |      | 5.3.3 Architectural Element Types                                                               |  |  |  |  |  |  |  |

|   | 5.4  | Modeling the Architectural Elements as Building Blocks                                          |  |  |  |  |  |  |  |

|   |      | 5.4.1 Packets                                                                                   |  |  |  |  |  |  |  |

|   |      | 5.4.2 Architecture                                                                              |  |  |  |  |  |  |  |

|   |      | 5.4.3 Processing Element                                                                        |  |  |  |  |  |  |  |

|   |      | 5.4.4 Communication Structure                                                                   |  |  |  |  |  |  |  |

|   |      | 5.4.5 Global Controller                                                                         |  |  |  |  |  |  |  |

|   |      | 5.4.6 Buffer                                                                                    |  |  |  |  |  |  |  |

|   |      | 5.4.7 Router                                                                                    |  |  |  |  |  |  |  |

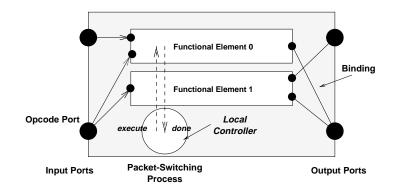

|   |      | 5.4.8 Functional Unit                                                                           |  |  |  |  |  |  |  |

|   |      | 5.4.9 Functional Element                                                                        |  |  |  |  |  |  |  |

|   |      |                                                                                                 |  |  |  |  |  |  |  |

|   |            | 5.4.10 Pipeline                                                                                                                 |   |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------|---|

|   |            | 5.4.11 Ports                                                                                                                    |   |

|   | 5.5        | Describing an Architecture Template                                                                                             |   |

|   |            | 5.5.1 Composition Rules                                                                                                         |   |

|   |            | 5.5.2 Architecture Description Language                                                                                         |   |

|   | 5.6        | Programming an Architecture Instance                                                                                            |   |

|   |            | 5.6.1 Application Network                                                                                                       |   |

|   |            | 5.6.2 Mapping                                                                                                                   |   |

|   |            | 5.6.3 Programming Model                                                                                                         | 3 |

|   |            | 5.6.4 Example                                                                                                                   |   |

|   | 5.7        | Conclusions                                                                                                                     | 5 |

| 6 | App        | lications 137                                                                                                                   | 7 |

|   | 6.1        | Stream-Based Applications                                                                                                       | 8 |

|   | 6.2        | Imperative Programming Languages                                                                                                |   |

|   | 6.3        | Stream-Based Functions                                                                                                          |   |

|   | 6.4        | The SBF Object         143                                                                                                      |   |

|   | 0.1        | 6.4.1 Functions                                                                                                                 | - |

|   |            | 6.4.2 Controller                                                                                                                |   |

|   | 6.5        | Example of an SBF Object                                                                                                        |   |

|   | 6.6        | Networks of SBF Objects                                                                                                         | - |

|   | 0.0        | 6.6.1 Composition of SBF Objects                                                                                                |   |

|   |            | $\mathbf{r}$                                                                                                                    |   |

|   | 67         |                                                                                                                                 |   |

|   | 6.7        | Related Work         150           6.7.1         Determine Market           150         150                                     |   |

|   |            | 6.7.1 Dataflow Models                                                                                                           |   |

|   |            | 6.7.2 Process Models                                                                                                            |   |

|   | <b>6</b> 0 | 6.7.3 Combined Dataflow/Process Models                                                                                          |   |

|   | 6.8        | Implementation of the SBF model                                                                                                 |   |

|   |            | 6.8.1 Host Language                                                                                                             |   |

|   |            | 6.8.2 Coordination Language                                                                                                     |   |

|   | 6.9        | Conclusions                                                                                                                     | 7 |

| 7 | Con        | struction of a Retargetable Simulator and Mapping 161                                                                           | 1 |

|   | 7.1        | Retargetable Architecture Simulators                                                                                            | 2 |

|   |            | 7.1.1 Requirements                                                                                                              | 3 |

|   | 7.2        | The Object Oriented Retargetable Simulator (ORAS)                                                                               | 3 |

|   | 7.3        | Development of ORAS                                                                                                             | 5 |

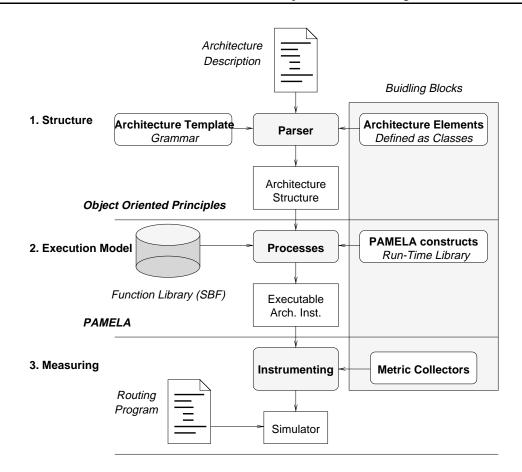

|   |            | 7.3.1 Step 1: Structure                                                                                                         | 5 |

|   |            | 7.3.2 Step 2: Execution Model                                                                                                   |   |

|   |            | 7.3.3 Step 3: Metric Collectors                                                                                                 |   |

|   | 7.4        | Mapping Applications                                                                                                            |   |

|   |            | 7.4.1         Mapping Approach         168           168         168         168                                                |   |

|   |            | 7.4.2 Matching Models of Architecture and Computation                                                                           |   |

|   |            | 7.4.2         Watering Woods of Areintecture and Computation 1         10           7.4.3         Control Hierarchy         170 |   |

|   | 7.5        | The Interface Between Application and Architecture                                                                              |   |

|   | 1.5        | 7.5.1 The Application – Architecture Interface                                                                                  |   |

|   |            |                                                                                                                                 |   |

|   |            | 7.5.2 Restricting Resources                                                                                                     | J |

|   | 7.6  | Construction Example                                                 |     |   |     |   | 175 |

|---|------|----------------------------------------------------------------------|-----|---|-----|---|-----|

|   | 7.7  | Related Work                                                         |     |   |     |   | 176 |

|   | 7.8  | Discussion on ORAS                                                   |     |   |     |   | 177 |

|   |      | 7.8.1 Building Blocks                                                |     |   |     |   | 178 |

|   |      | 7.8.2 High-level Primitives                                          |     |   |     |   | 178 |

|   |      | 7.8.3 Interpreted Model                                              |     |   |     |   | 178 |

|   |      | 7.8.4 Limitations                                                    |     |   |     |   | 178 |

|   | 7.9  | A Generic Approach for a Retargetable Simulator                      |     |   |     |   | 179 |

|   |      | 7.9.1 Step 1: Structure                                              |     |   |     |   | 179 |

|   |      | 7.9.2 Step 2: Execution Model                                        |     |   |     |   | 179 |

|   |      | 7.9.3 Step 3: Metric Collectors                                      |     |   |     |   | 180 |

|   |      | 7.9.4 Mapping                                                        |     |   |     |   | 180 |

|   | 7.10 | Conclusions                                                          |     |   |     |   | 180 |

|   |      |                                                                      |     |   |     |   |     |

| 8 |      | ign Space Exploration                                                |     |   |     |   | 183 |

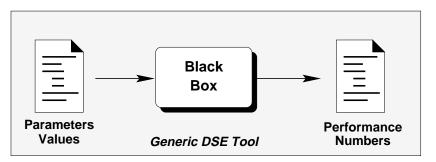

|   | 8.1  | The Acquisition of Insight                                           |     |   |     |   | 184 |

|   | 8.2  | Design Space Exploration                                             |     |   |     |   | 185 |

|   | 8.3  | Design Space Exploration Environment                                 |     |   |     |   | 186 |

|   |      | 8.3.1 Spanning the Design Space                                      |     |   |     |   | 186 |

|   |      | 8.3.2 Construction of the Response Surface Model                     |     |   |     |   | 188 |

|   |      | 8.3.3 Data Management and Data Consistency                           |     |   |     |   | 189 |

|   |      | 8.3.4 Parameterizing the Architecture Description                    |     |   |     |   | 189 |

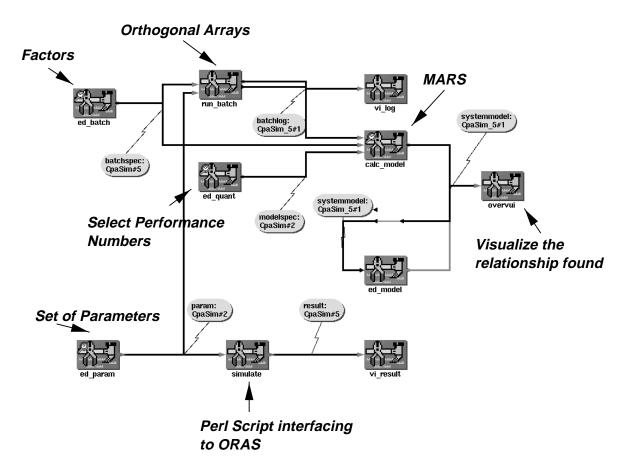

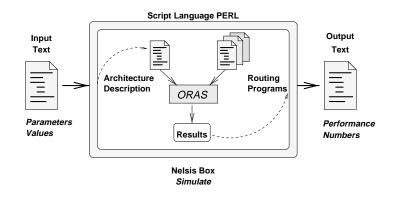

|   | 8.4  | Integrating ORAS within the Generic DSE Environment                  |     |   |     |   | 192 |

|   |      | 8.4.1 Selecting Parameter Values                                     |     |   |     |   | 192 |

|   |      | 8.4.2 Running the Y-chart in the DSE Environment                     |     |   |     |   | 192 |

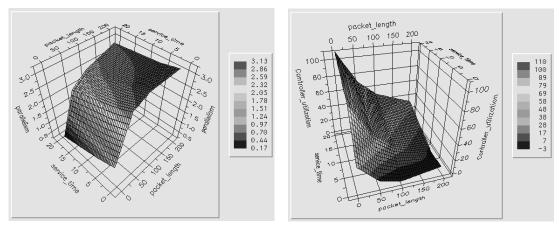

|   |      | 8.4.3 Creating Response Surface Model                                |     |   |     |   | 193 |

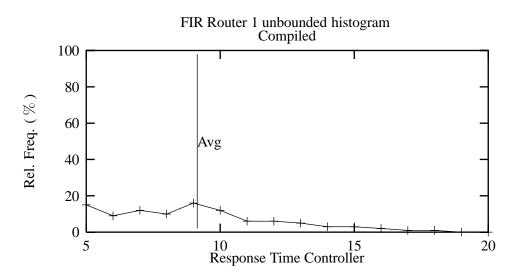

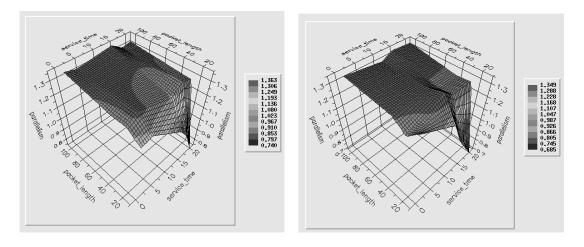

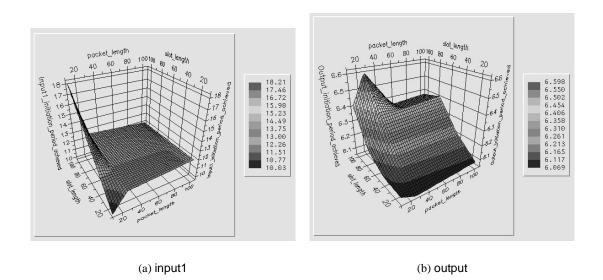

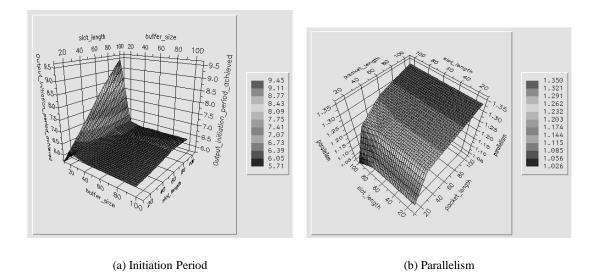

|   | 8.5  | An Example of Design Space Exploration                               |     |   |     |   | 194 |

|   | 8.6  | Related Work                                                         |     |   |     |   | 195 |

|   | 8.7  | Conclusions                                                          | • • | · | ••• | • | 197 |

| 9 | Desi | ign Cases                                                            |     |   |     |   | 201 |

|   | 9.1  | Motivation                                                           |     |   |     |   | 202 |

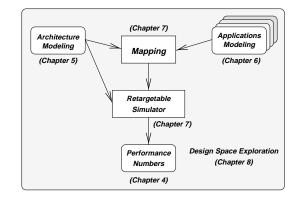

|   |      | 9.1.1 Application Characteristics                                    |     |   |     |   | 202 |

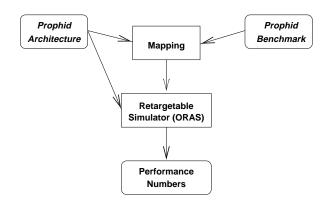

|   | 9.2  | Case 1: The Prophid Architecture (Philips Research)                  |     |   |     |   | 203 |

|   |      | 9.2.1 Prophid Architecture                                           |     |   |     |   | 203 |

|   |      | 9.2.2 Prophid Benchmark                                              |     |   |     |   | 203 |

|   |      | 9.2.3 The Use of the Y-chart in the Prophid Case                     |     |   |     |   | 204 |

|   |      | 9.2.4 Issues in Modeling the Prophid Architecture                    |     |   |     |   | 206 |

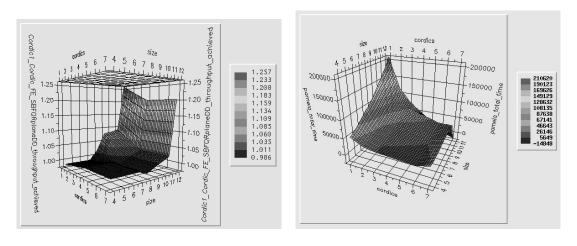

|   |      | 9.2.5 Results                                                        |     |   |     |   | 208 |

|   |      | 9.2.6 Conclusions                                                    |     |   |     |   | 210 |

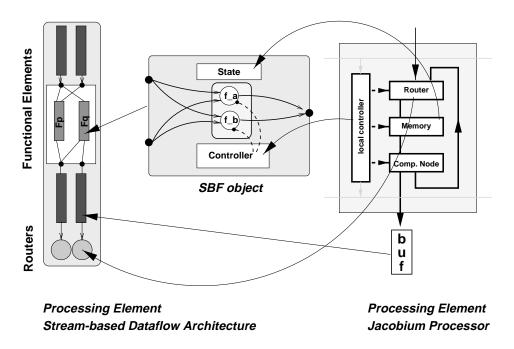

|   | 9.3  | Case 2: The Jacobium Processor (Delft University of Technology)      |     |   |     |   | 210 |

|   |      | 9.3.1 The Jacobium Processor Architecture                            |     |   |     |   | 211 |

|   |      | 9.3.2 Jacobium Applications                                          |     |   |     |   | 213 |

|   |      | 9.3.3 The Use of the Y-chart Approach in the Jacobium Processor Case |     |   |     |   | 213 |

|   |      | 9.3.4 Deriving a Network of SBF Objects from a Dependence Graph      |     |   |     |   | 216 |

|   |      | 9.3.5 Results                                                        |     |   |     |   | 219 |

|   |      | 9.3.6 Conclusions                                                    |     |   |     |   | 221 |

|   |      |                                                                      | - • | • | • • | • |     |

| 10 | Sum                                     | mary & Conclusions                             | 225 |  |  |  |  |

|----|-----------------------------------------|------------------------------------------------|-----|--|--|--|--|

|    | 10.1 Discussion of the Y-chart Approach |                                                |     |  |  |  |  |

|    |                                         | 10.1.1 Significant Effort                      | 226 |  |  |  |  |

|    |                                         | 10.1.2 Characteristics of the Y-chart Approach | 227 |  |  |  |  |

|    |                                         | 10.1.3 Structuring the Design Process          | 227 |  |  |  |  |

|    |                                         | 10.1.4 Multi-Disciplinary Teams                | 228 |  |  |  |  |

|    | 10.2                                    | Further Research                               | 228 |  |  |  |  |

|    | 10.3                                    | Availability of Software                       | 229 |  |  |  |  |

| A  | Arch                                    | nitecture Template in BNF                      | 231 |  |  |  |  |

| B  | Pictu                                   | ıre in Picture Example                         | 235 |  |  |  |  |

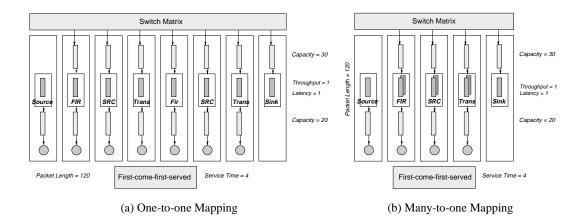

|    | <b>B</b> .1                             | One-to-one Architecture Instance               | 235 |  |  |  |  |

|    |                                         | B.1.1 Architecture Description                 | 236 |  |  |  |  |

|    |                                         | B.1.2 Mapping                                  | 238 |  |  |  |  |

|    | B.2                                     | Many-to-one Architecture Instance              | 239 |  |  |  |  |

|    |                                         | B.2.1 Architecture Description                 | 239 |  |  |  |  |

|    |                                         | B.2.2 Mapping                                  | 241 |  |  |  |  |

| С  | Limi                                    | itations of the RTL                            | 243 |  |  |  |  |

|    | C.1                                     | State of the System                            | 243 |  |  |  |  |

|    |                                         | C.1.1 Polling                                  | 243 |  |  |  |  |

|    |                                         | C.1.2 Priority Scheduling                      | 244 |  |  |  |  |

|    | C.2                                     | Implementing Polling in the RTL                | 244 |  |  |  |  |

|    | C.3                                     | Modeling the TDM global controller             | 245 |  |  |  |  |

|    |                                         | C.3.1 TDM Controlled Routers                   | 246 |  |  |  |  |

|    | C.4                                     | How VHDL differs from the RTL                  | 246 |  |  |  |  |

| Ac | know                                    | ledgments                                      | 253 |  |  |  |  |

| Sa | menv                                    | atting                                         | 255 |  |  |  |  |

| Cu | rricu                                   | lum Vitae                                      | 257 |  |  |  |  |

## **Chapter 1**

## Introduction

#### Contents

| 1.1 | Motiv                                   | ation                                                  |  |  |  |  |  |

|-----|-----------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| 1.2 | 1.2 Video Signal Processing in a TV-set |                                                        |  |  |  |  |  |

|     | 1.2.1                                   | TV-set                                                 |  |  |  |  |  |

|     | 1.2.2                                   | Video Processing Architectures in the TV of the Future |  |  |  |  |  |

|     | 1.2.3                                   | Stream-Based Dataflow Architecture                     |  |  |  |  |  |

| 1.3 | Desig                                   | n Space Exploration                                    |  |  |  |  |  |

| 1.4 | Main                                    | Contributions of Thesis                                |  |  |  |  |  |

| 1.5 | Outlin                                  | ne of the Thesis                                       |  |  |  |  |  |

THE increasing digitalization of information in text, speech, video, audio and graphics has resulted in a whole new variety of digital signal processing (DSP) applications like compression and decompression, encryption, and all kinds of quality improvements [Negroponte, 1995]. A prerequisite for making these signal processing applications available to the consumer market is their cost-effective realization into silicon. This leads to a demand for new application-specific architectures that are increasingly *programmable* i.e., architectures that can execute a set of applications instead of only one specific application. By reprogramming these architectures, they can execute other applications with the same resources, which makes these programmable architectures cost-effective. In the near future, these architectures should find their way into consumer products like TV-sets, set-top boxes, multi-media terminals, and other multi-media products, as well as in wireless communication and low cost radar systems.

The trend toward architectures that are more and more programmable represents, as argued by Lee and Messerschmitt [1998], the first major shift in electrical engineering since the transitions from analog to digital electronics and from vacuum tubes to semiconductors. However, general and structured approaches are lacking for designing application-specific architectures that are sufficiently programmable.

The current practice is to design application-specific architectures at a detailed level using hardware description languages like VHDL [1993] (Very high speed IC hardware description Language) or Verilog. A consequence of this approach is that designers work with very detailed descriptions of architectures. The level of detail involved limits the design space of the architectures that they can explore, which gives them little freedom to make trade-offs between programmability, utilization of resources, and silicon area. Because designers cannot make these trade-offs, designs end up underutilizing their resources and silicon area and are thus unnecessarily expensive, or they cannot satisfy the imposed design objectives.

The development of programmable architectures that execute widely different applications has already been being worked on for decades in the domain of general-purpose processors. These processors can execute a word-processing application or a spreadsheet application or can even simulate some complex physical phenomenon, all on the same piece of silicon. Currently, these processors are designed by constructing performance models of processors at different levels of abstraction ranging from instruction level models to Register Transfer Level (RTL) models [Bose and Conte, 1998; Hennessy and Heinrich, 1996]. These *performance models* can be evaluated to provide data for various *performance metrics* of a processor, like resource utilization and compute power while processing a workload. A workload is typically a suite of *benchmarks*, i.e., a set of typical applications a processor should execute. Measuring the performance of a processors at various levels of detail and to make trade-offs at the different levels between, for example, the utilization of resources and performance of processors. Moreover, quantitative data gives designers insight, at various levels of detail, into how to further improve architectures and serves as an objective basis for discussion of possible architecture improvements.

The benchmark approach practiced in general-purpose processor architecture design leads to finely tuned architectures targeted at particular markets. When the benchmark approach was initially introduced at the beginning of the 1980s, it revolutionized general-purpose processor design, which resulted in the development of RISC-style processors [Patterson, 1985]. These processor architectures were smaller, faster, less expensive and easier to program than any conventional processor architecture of that time [Hennessy and Patterson, 1996].

General-purpose processors, although programmable, are not powerful enough to execute the digital signal processing applications we are aiming at, as we will explain soon. Special applicationspecific architectures are therefore required that are nonetheless programmable to some extent. The benchmark approach used in the design of general-purpose processors is also useful in the design of the programmable application-specific architectures emerging now, as we show in this thesis. We will develop and implement in this thesis a benchmark approach, which we call the Y-chart approach, for a particular class of programmable application-specific architecture called *Stream-Based Dataflow Architecture*. The benchmark approach we develop results in an environment in which designers are able to perform design space exploration for the stream-based dataflow architecture at a level of abstraction that is higher than that offered by standard hardware description languages.

In Section 1.1 of this chapter we explain further why programmable application-specific architectures will emerge for digital signal processing applications. Following this, in Section 1.2 we discuss as an example the video signal processing architecture in a modern TV-set. Based on this example, we illustrate how the trend towards programmable architectures will affect the next generation of TV-sets and explain why general-purpose processors are not capable of providing the required performance at acceptable cost. We focus on the stream-based dataflow architecture in TV-sets. In Section 1.3 we indicate how we are going to explore the design space of this architecture at a high level of abstraction. This chapter concludes with the statement of the main contributions of this thesis in Section 1.4 and the further outline for the thesis in Section 1.5.

### **1.1 Motivation**

New advanced digital signal processing applications like signal compression and decompression, encryption, and all kinds of quality improvements become feasible on a single chip because the number of transistors on a single die is still increasing, as predicted by Moore's law. Digital signal processing applications involve *real-time* processing, which implies that these applications take in and produce samples at a particular guaranteed rate, even under worst-case conditions. In addition, these applications are very demanding with respect to *computational power*, i.e., the number of operations performed in time, and *bandwidth*, i.e., the amount of data transported in time.

Architectures that realize the new applications cost-effectively in silicon must be able first of all to deliver enough processing power and bandwidth to execute the applications and secondly to satisfy the real-time requirements of the applications. The design of such new architecture configurations is becoming an increasingly intricate process. Architectures are becoming increasingly programmable so that they can support *multi-functional* products as well as *multi-standard* products (like a mobile telephone operational worldwide). In the design of these architectures, it is no longer the performance of a single application that matters, but the performance of a *set of applications*. This impedes the design of architectures that must satisfy all the given constraints such as real-time processing, utilization of the resources, and programmability.

Before we look in more depth into the design problems of these new architectures, we illustrate the trend towards more programmable application-specific architectures by looking at the video signal processing architecture inside a modern television. In this domain, the need for architectures that can execute a set of applications is clearly present.

## **1.2 Video Signal Processing in a TV-set**

The trend towards devising new signal processing architectures that are programmable is clearly visible in the domain of consumer market TV-sets, where the digital revolution started in the 1980s and early 1990s. In this period, the signal processing architecture inside a TV-set moved from analog processing to digital processing, whereby analog functions were replaced by digital functions. The all-digital TV architecture together with the expected continuation of transistor miniaturization in the semiconductor industry has led to increased demand for new innovative signal processing architectures.

#### 1.2.1 TV-set

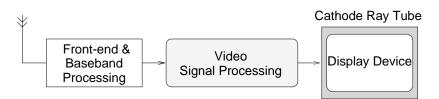

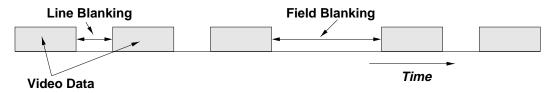

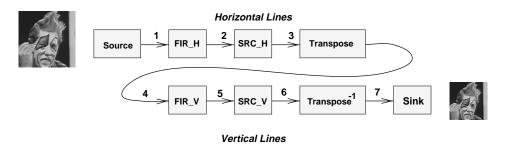

The signal path within a TV-set consists of three sections: a *front-end and baseband processing section*, a *video signal processing section*, and a *display section*, as shown in Figure 1.1. The first section transforms a TV-signal coming from an outside source like an aerial antenna into a signal that the display section visualizes on a display device, for example a Cathode Ray Tube (CRT). In between these two sections is an analog video signal processing section that makes a received signal suitable for display.

As the video signal processing section evolves from being analog to fully digital, a whole range of new applications becomes available through digital signal processing. Examples of new digital applications that improve the quality of images are luminance peaking [Jaspers and de With, 1997], noise reduction, and ghost image cancellation. Examples of complete new applications are picture reduction (Picture in Picture), picture enlargement (Zoom) [Janssen et al., 1997], and motion compensated 100Hz image conversions [de Haan et al., 1996].

**Figure 1.1**. The signal path within a TV-set consists of three sections: a *front-end and baseband processing section*, a *video signal processing section*, and a *display section*.

A TV-set must also be compatible with an increasing variety of standards. Signals containing content to be displayed may be delivered through many different sources, like cable TV, a satellite dish, a computer, video recorder (VCR), or a set-top box. Traditionally these formats have complied with conventional formats like NTSC (National Television System Committee), PAL (Phase Alternating Line), or SECAM (Sequentiel à Mémoire), but increasingly often they are now also complying with emerging standards like various types of MPEG (Moving Picture Expert Group) and computer standards like SVGA (Super Video Graphics Array).

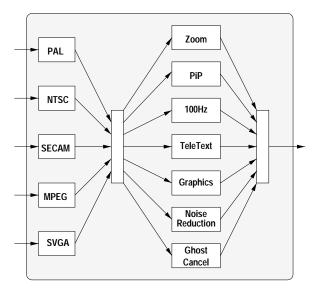

The increasing demand for new digital applications by consumers and the need for TV-sets to comply to different standards has made a more complex video signal processing section necessary in TV-sets [Claasen, 1993]. The video signal processing section of a modern high-end TV-set is shown in Figure 1.2. Each of the applications shown has its own hardware processing unit, When new applications are added, new hardware units are incorporated into the video signal processing architecture to support them. Since the customer does not select all applications at the same time, the architecture uses these units uneconomically.

Figure 1.2. Video signal processing section of a modern high-end TV-set.

Because each hardware unit is dedicated to one particular application, it is not possible for applications to share hardware units. However, if the hardware units were made less dedicated (which we discuss later in this chapter), hardware units could be used to support more than one application. These programmable architectures of tomorrow could be reprogrammed to execute other applications with the same amount of resources, thus improving the utilization of silicon in implementing architectures. Thus, these architectures become cost effective for a set of applications.

#### **1.2.2** Video Processing Architectures in the TV of the Future

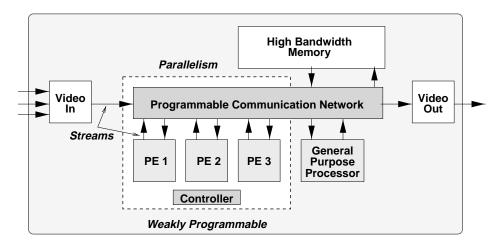

The architecture most likely to be found in the TV-set of tomorrow [Claasen, 1993] will look similar to the structure illustrated in Figure 1.3. This architecture is built around a programmable communication network to which various elements connect. The video-in processor consists of several input channels. The video-out processor takes an output signal to the display section. A collection of processing elements (PEs) operate as hardware-accelerators, and a general purpose processor and a large high-bandwidth memory are present as well. The set of processing elements have their own controller and operate very independently (but not completely) of the general-purpose processor.

Figure 1.3. TV architecture of tomorrow.

The architecture in Figure 1.3 combines two architecture concepts: a general-purpose processor and the architecture enclosed by the dashed line. These two concepts are needed because of the large variety of timing constraints present in a TV-set, as we will show. The general-purpose processor processes reactive tasks (e.g., a user pressing on the volume button on the remote control) and control tasks (e.g., controlling the menus displayed on the screen and their functions). The dedicated processing elements, on the other hand, execute data processing tasks, i.e., the digital signal processing applications.

The large variations in timing constraints are caused by the structure of TV-signals. For example, a standard PAL video signal consists of a sequence of frames presented at a rate of 25 interlaced video *frames* per second. Each frame consists of two *fields*: an even field containing the even video lines and an odd field containing the odd video lines. A field has 312 video *lines*, and each line consists of 864 video *pixels*. Algorithms that operate on PAL video signals with different repetition periods – either pixels, lines, fields, or frames – result in very different computational requirements. Suppose an algorithm consists of 300 RISC-like operations and operates periodically on pixels, lines, fields, or frames. The vastly different computational requirements are given in Table 1.1. An algorithm operating at a field rate would perform  $50 \times 300$ , or 15,000 operations per second. An algorithm operating at a pixel rate would perform  $13.5M \times 300$  operations per second, which is 4 Giga operations per second.

A general-purpose processor (e.g., a RISC processor) is considered powerful enough to execute

| Type of repetition rate     | Computational requirements               |  |  |  |

|-----------------------------|------------------------------------------|--|--|--|

| for performing an operation | (Operations per second)                  |  |  |  |

| Pixels                      | $4.05 \times 10^9 = 300 \times 13500000$ |  |  |  |

| Lines                       | $4.8 \times 10^6 = 300 \times 16000$     |  |  |  |

| Fields                      | $15 \times 10^3 = \qquad 300 \times 50$  |  |  |  |

| Frames                      | $7.5 \times 10^2 = 300 \times 25$        |  |  |  |

**Table 1.1**. Computational requirements for different types of repetition rates for performing operations.

periodically scheduled algorithms with repetition cycles based on field or frame rates and it can also perform all kinds of reactive and control tasks. The efficiency of general-purpose processors, as measured in terms of performance per dollar, is increasing at a dazzling rate [Hennessy and Patterson, 1996]. However, they are still not powerful enough to execute periodically scheduled high-quality video algorithms with repetition cycles based on pixel or line rates.

It is inevitable that architectures used in TV-sets and in computers will eventually be merged to create new products like the PCTV [Rose, 1996] that are centered around one or more powerful general-purpose processors. Many high-end general-purpose processors already demonstrate a clear trend towards real-time processing using special multi-media instructions [Diefendorff and Dubey, 1997]. However, these general-purpose processors will not be able to furnish the processing power and communication bandwidth in the near future that is required by current and forthcoming TV applications. Consequently, at least for the coming decade, TV architectures will use a general-purpose processor in conjunction with a special architecture for the high-performance, real-time video processing.

#### 1.2.3 Stream-Based Dataflow Architecture

The architecture enclosed by the dashed line in Figure 1.3 describes a programmable, applicationspecific architecture for high-performance, real-time video applications. We call this architecture *Stream-Based Dataflow Architecture* and we consider this architecture and its design in detail in this thesis.

A *Stream-Based Dataflow Architecture* consists of a global controller, a communication structure and a set of parallel-operating processor elements that are weakly programmable. These processing elements operate on streams that they exchange among each other via the communication structure under control of the global controller. The architecture exploits the following characteristics so as to be programmable, efficient, and able to satisfy real-time constraints.

- **Stream-based processing** The processing elements operate on streams: these are a natural form with which to represent video as a one-dimensional sequence of video pixels [Watlington and Michael Bove Jr, 1997].

- **Coarse-grained parallelism** The processing elements exploit inherent coarse-grained parallelism available within video applications by executing coarse-grained functions to achieve the required computational performance.

**Weakly Programmable** The processing elements implement a limited set of coarse-grained functions that provide the processing elements with the flexibility required to support a set of applications.

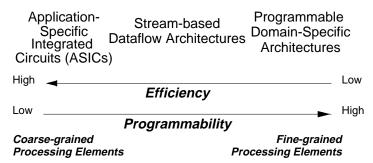

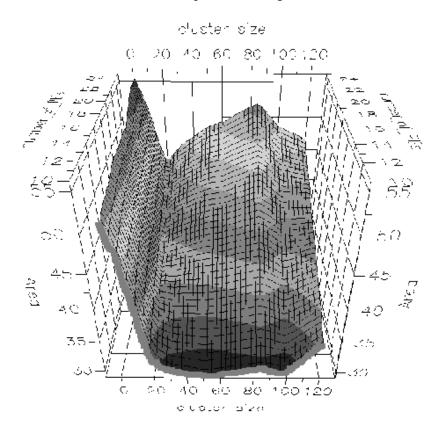

The granularity of the functions implemented by the processing elements highly influences the efficiency of stream-based dataflow architectures. The granularity of the functions has two extremes, as illustrated in Figure 1.4.

At one end of the spectrum, there are Application Specific Integrated Circuits (ASICs). Here, each ASIC implements one video application like luminance peaking, noise reduction, or picture in picture. An ASIC can only execute one application very efficiently in terms of silicon use. At the other end of the spectrum are programmable domain specific architectures like the VSP [Vissers et al., 1995] or Paddi [Chen, 1992]. These architectures use processing elements that implement small sets of fine-grained functions like add, subtract, and compare. These fine-grained functions allow the architectures to execute a wide range of video applications belonging to a specific application domain while satisfying real-time constraints. However, in order to support this programmability, these architectures dedicate a substantial part of their silicon area to control and communication and less to the actual computation.

For some video applications a gap of a factor of ten to twenty is found in silicon efficiency between an ASIC solution and a programmable solution [Lippens et al., 1996, 1991]. If multiple applications execute at the same time, a collection of ASICs results in the most efficient solution. However, for a given set of applications of which only one or a few execute simultaneously, the efficiency is no longer that high. In that case, a domain-specific programmable architecture is not efficient either, because it possesses more flexibility than required, i.e., the architecture can execute more applications than are present in the set of applications. This surplus of programmability is present at the expense of extra silicon.

**Figure 1.4**. The relationship between granularity of the processing elements and the efficiency and programmability for high-performance, real-time signal processing applications. At one extreme of the spectrum, we find application-specific architectures that use very coarse-grained processing elements. They are very efficient but cannot be programmed. At the other end of the spectrum, we find programmable domain-specific architectures that use very fine-grained processing elements. They are highly programmable but have a low efficiency. Stream-based dataflow architectures result in the best balance between efficiency and programmability.

Lieverse et al. [1997] have investigated the relationship between the granularity of the processing elements and the efficiency and programmability of a stream-based dataflow architecture. For a limited set of applications, coarse-grained processing elements (i.e., processing elements implementing coarse-grained functions) result in the best balance between efficiency and programmability for high-performance, real-time signal processing applications. Therefore, we investigate stream-based dataflow architectures that make use of coarse-grained processing elements.

### **1.3 Design Space Exploration**

In the design of programmable application-specific architectures like the stream-based dataflow architecture, a designer has to make many choices, like the granularity of the functions that the processing elements implement. Other choices include the number of processing elements to use or how much bandwidth to allocate to the communication network. These and many more choices have an effect on the overall performance of architectures in terms of utilization of the resources and throughput of the various processing elements. Furthermore, because the architecture has to execute a set of applications, particular choices might be excellent for one application in the set, but bad for another.

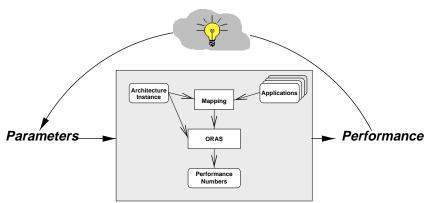

Nevertheless, a designer has to make choices such that the performance of the architecture is satisfactory for the set of applications while being cost effective. To achieve this goal, a designer has to make *trade-offs*, i.e., weigh one choice against another and come to a compromise. A designer must know what the design space of architectures looks like in order to make trade-offs. He acquires this knowledge by *exploring* how a particular performance metric depends on a particular parameter.

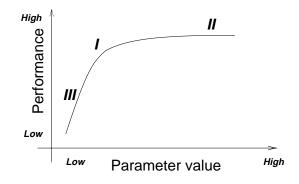

Design space exploration typically results in graphs like the one shown in Figure 1.5. It shows a simplified, idealized relationship between a measured performance of the architecture for a range of parameter values that each represent particular choices.

**Figure 1.5**. The relationship between a measured performance in the architecture and a range of parameter values. Point I indicates the best trade-off between a particular performance and parameter values. Point II shows a marginal increase of the performance at a large cost and point III shows a deterioration of the performance.

In such graphs, there is often a point (I) representing the best trade-off between a particular performance and parameter value; it is this point, the so-called knee, that a designer seeks. Selecting a larger parameter value (i.e., closer to II) would result in a marginal increase in the performance at a large cost. On the other hand, selecting a lower parameter value (i.e., closer to III) would result in a deterioration of the performance.

We observed designs of programmable application-specific architectures at both Philips Research and Delft University of Technology. Based on these observations, we conclude that it is current practice to design these architectures at a low level of detail. Architectures are described in a standard hardware description language like VHDL or Verilog and consequently the designer ends up with too much detail. The level of detail involved limits the design space of these architectures that the designer can explore to look for better trade-offs. Therefore, a designer has difficulty finding a balance among the many choices present in architectures during the design process. This makes it hard to produce architectures that are both cost effective and programmable enough to support a set of applications.

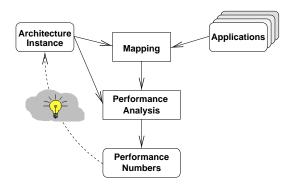

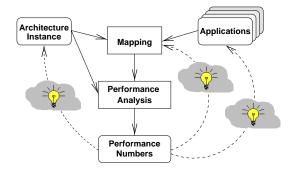

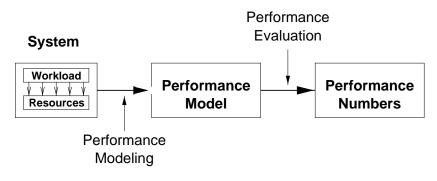

In this thesis we present a design approach called the "Y-chart approach" that overcomes the limitations introduced by the low level of detail currently involved in the design of programmable architectures and which makes it possible to make better trade-offs in architectures. This approach leads to an environment in which designers can first exercise architecture design, making design choices in architectures quantitative using *performance analysis*.

This involves the modeling of architectures to determine a performance model and the evaluation of this performance model to determine performance numbers, thus providing data for various performance metrics of a processor. In addition, by systematically changing design choices in a Y-chart environment, a designer should be able to systematically explore part of the design space of an architecture. This exploration provides the designer with the insight required for making the trade-offs necessary for a good architecture for a given set of applications.

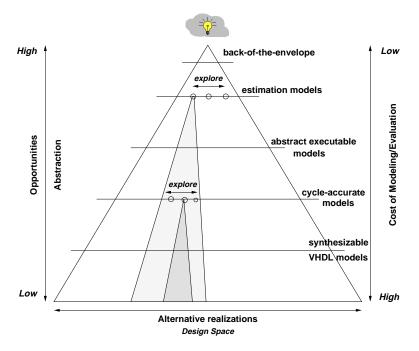

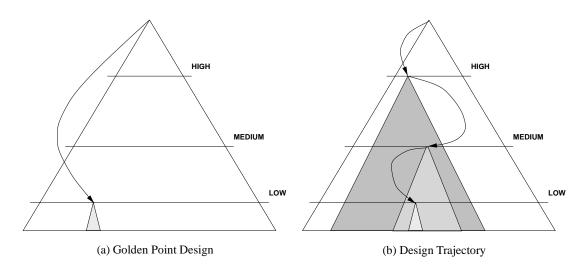

Performance analysis can take place at different levels of detail and designers should exploit these different levels to narrow down the design space of architectures in a stepwise fashion. A Y-chart environment is used in each step, but at different levels of detail. Therefore, when the modeling and evaluation of architectures is relatively inexpensive, a large part of the design space can be explored. By the time the modeling of an architecture as well as the evaluation of this model become expensive, the design space has been reduced considerably and it contains the interesting design points.

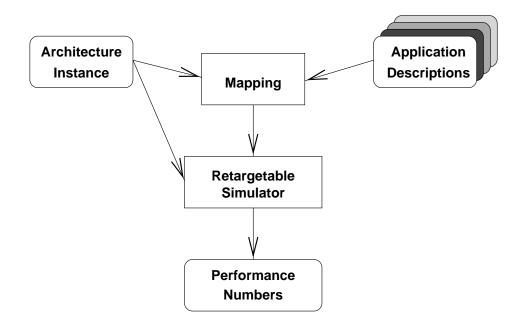

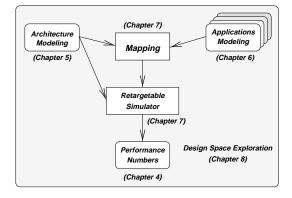

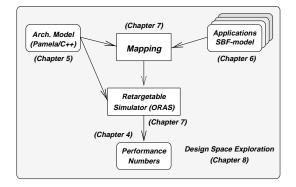

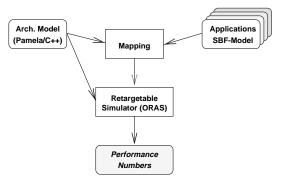

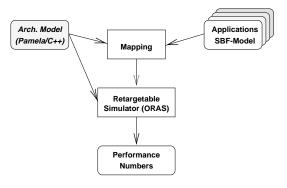

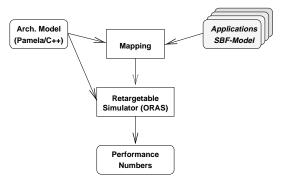

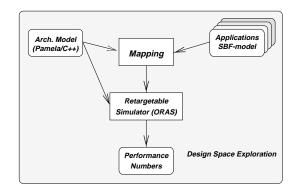

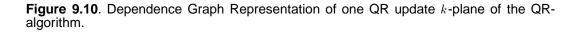

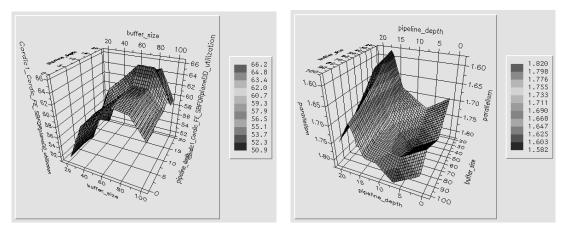

**Figure 1.6**. The Y-chart environment we develop in this thesis. The highlighted components of the chart are labeled with references to the chapters in which they are elaborated.

The Y-chart approach structures the design process of programmable architectures. It takes into account right from the beginning the three core issues that play a role in finding good programmable application-specific architectures, i.e., the architecture, the mapping, and the set of applications.

A general outline for the Y-chart environment as we will develop it in this thesis for stream-based dataflow architectures in order to explore their design space is shown in Figure 1.6. We will do this at a level of abstraction higher than that offered by standard hardware description languages.

## 1.4 Main Contributions of Thesis

The main contributions of this thesis are:

**Y-chart Approach** The pivotal idea in this thesis is to provide a means with which the effect of design choices on architectures can be quantified. This resulted in the formulation of the Y-chart approach, which quantifies design choices by measuring the performance.

We implemented the Y-chart approach in a Y-chart environment for the class of stream-based dataflow architectures. This led to the following contributions:

- Architecture Template for Stream-based Dataflow Architectures We present the stream-based dataflow architecture as a class of architectures. We show that all choices available within this class of architectures can be described by means of an architecture template that has a well defined design space. We derive architecture instances from the architecture template.

- **Modeling Architectures in a Building Block Approach** We use a high-level performance-modeling tool to render performance analysis at a high abstraction level. Using this method, we model the complete class of stream-based dataflow architectures while still obtaining cycle-accurate results. We use object oriented programming techniques extensively together with the performance-modeling tool to construct building blocks. Using these building blocks, we construct executable architecture instances of the architecture template of stream-based dataflow architectures.

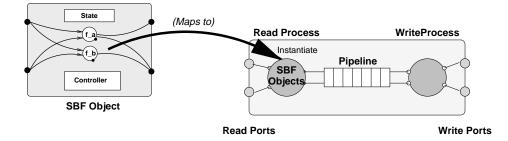

- Stream-based Functions (SBF) Model We develop a new model of computation: the Stream-based Functions (SBF) Model. This model combines Kahn Process Networks [Kahn, 1974] with the a specialization of the Applicative State Transition (AST) Model proposed initially by Backus [1978]. The SBF model is well suited for describing digital signal processing applications at different levels of granularity, ranging from fine-grained to coarse-grained. We also develop a simulator called SBFsim for the SBF model.

- **ORAS** We develop the Object Oriented Retargetable Simulator (ORAS). Because ORAS is retargetable, it can derive a full functional simulator for all feasible architectures from the class of stream-based dataflow architectures. The derived simulator operates very fast in terms of real computer time while it also executes the correct functional behavior of an application. The execution speed is a prerequisite to performing an exploration of the design space of the class of stream-based dataflow architectures in a limited amount of time.

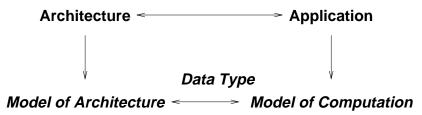

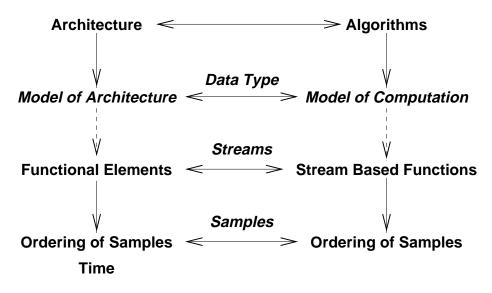

- **Mapping Approach** We introduce the notion of the model of architecture. Using this notion, we formulate a mapping approach in which we postulate that the model of computation should match the model of architecture of stream-based dataflow architectures. Only in this way is a smooth mapping possible. Moreover, it leads to an interface between applications and architecture. This interface permits the execution of applications onto an architecture instance without its being necessary to modify the original application when mapping the application onto an architecture instance.

- **Design Space Exploration** We use a generic design space exploration environment to perform an exploration of stream-based dataflow architectures. We also formulate the problem of selecting a set of parameters that result in a particular architecture which satisfies the design objectives for a set of applications.

- **Different Design Cases** We use the Y-chart approach in two different design cases of programmable architectures. One design case is the *Prophid* video-processor architecture [Leijten et al., 1997]

for high-performance video applications and the other is the *Jacobium* processor architecture [Rijpkema et al., 1997] for array signal processing applications.

### **1.5** Outline of the Thesis

The organization of this thesis is as follows. We present the class of stream-based dataflow architectures in detail and formulate the main problem statement in Chapter 2. Our solution approach – the Y-chart approach – is presented and discussed in Chapter 3. The chapters that follow each discuss a particular aspect of the Y-chart environment for the class of stream-based dataflow architectures.

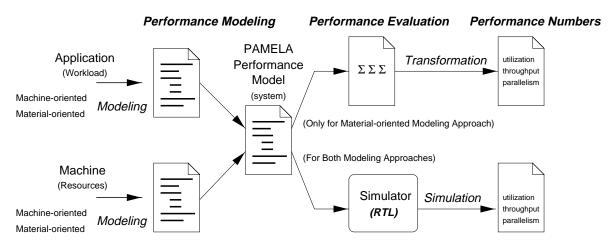

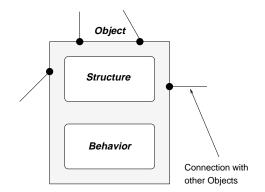

We explain what performance analysis entails in Chapter 4. We look into the aspects that determine the performance of a system, thus laying the foundation for performance analysis at a high level of abstraction. We use a high-level performance analysis method to carry out the performance analysis. Using this method, we set up an object oriented modeling approach leading to the notion of building blocks.

In Chapter 5, we look at how to model stream-based dataflow architectures using the building blocks discussed in Chapter 4. We construct the building blocks of the stream-based dataflow architecture in detail. We explain how we describe a class of architectures using a parser. Finally, we explain how to program stream-based dataflow architectures such that they execute a particular application.

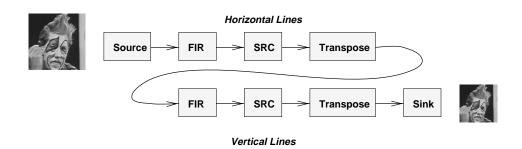

To model applications, we introduce a new model of computation, called *Stream-Based Functions* (SBF). In Chapter 6, we explain what the SBF Model of computation comprises. We also explain how the SBF Model is embedded in other well-established models of computations. How we implemented this model of computation using C++ and Multi-threading is also described.

In Chapter 7 we combine all these aspects to construct the *Object oriented Retargetable Architecture Simulator* (ORAS). We combine the work on architecture modeling presented in Chapter 5 with the work on application modeling in Chapter 6 to construct a retargetable simulator that executes at high speed. We also look in detail how we can easily map an application onto an architecture instance.

In Chapter 8 we explain what design space exploration (DSE) implies. We embed the ORAS developed in Chapter 7 in a generic design space exploration environment. We elaborate on the statistical tools that the generic DSE environment uses to perform design space exploration efficiently. We also explain how we actually embed the ORAS in the generic DSE environment.

We investigate in Chapter 9 two cases in which a programmable architecture is developed and we use in their design the Y-chart environment developed in this thesis. One case concerns the Prophid architecture for high-performance video application developed at Philips Research; the other concerns the Jacobium architecture for a set of array signal processing applications developed at the Delft University of Technology.

We conclude this thesis in Chapter 10 with our conclusions.

### **Bibliography**

- John Backus. Can programming be liberated from the von Neumann style? A functional style and its algebra of programs. *Communications of the ACM*, 21(8):613 641, 1978.

- Pradip Bose and Thomas M. Conte. Performance analysis and its impact on design. *IEEE Computer*, 31(5):41 49, 1998.

- D.C. Chen. *Programmable Arithmetic Devices for High Speed Digital Signal Processing*. PhD thesis, University of California at Berkeley, California, Department of Electrical Engineering and Computer Science, 1992.

- T.A.C.M. Claasen. Technical and industrial challenges for signal processing in consumer electronics: A case study on TV applications. In *Proceedings of VLSI Signal Processing, VI*, pages 3 – 11, 1993.

- G. de Haan, J. Kettenis, and B. Deloore. IC for motion compensated 100hz TV, with smooth motion movie-mode. In *IEEE Transactions on Consumer Electronics*, volume 42, pages 165 174, 1996.

- Keith Diefendorff and Pradeep K. Dubey. How multimedia workloads will change processor design. *IEEE Computer*, 30(9):43 45, 1997.

- John Hennessy and Mark Heinrich. Hardware/software codesign of processors: Concepts and examples. In Giovanni De Micheli and Mariagiovanna Sami, editors, *Hardware/Software Codesign*, volume 310 of Series E: Applied Sciences, pages 29 44. NATO ASI Series, 1996.

- John L. Hennessy and David A. Patterson. *Computer Architectures: A Quantitative Approach*. Morgan Kaufmann Publishers, Inc., second edition, 1996.

- Johan G.W.M. Janssen, Jeroen H. Stessen, and Peter H.N. de With. An advanced sampling rate conversion algorithm for video and graphics signals. In *IEE Sixth International Conference on Image Processing and its Applications*, Dublin, 1997.

- Egbert G.T. Jaspers and Peter H.N. de With. A generic 2-D sharpness enhancement algorithm for luminance signals. In *IEE Sixth International Conference on Image Processing and its Applications*, Dublin, 1997.

- Gilles Kahn. The semantics of a simple language for parallel programming. In *Proc. of the IFIP Congress* 74. North-Holland Publishing Co., 1974.

- Edward A. Lee and David G. Messerschmitt. Engineering and education for the future. *IEEE Computer*, 31(1):77 85, 1998.

- Jeroen A.J. Leijten, Jef L. van Meerbergen, Adwin H. Timmer, and Jochen A.G. Jess. Prophid: A heterogeneous multi-processor architecture for multimedia. In *Proceedings of ICCD*'97, 1997.

- P. Lieverse, E.F. Deprettere, A.C.J. Kienhuis, and E.A. de Kock. A clustering approach to explore grain-sizes in the definition of weakly programmable processing elements. In *Proceedings of the IEEE Workshop on Signal Processing Systems*, pages 107 – 120, De Montfort University, Leicester, UK, 1997.

- Paul Lippens, Bart De Loore, Gerard de Haan, Piet Eeckhout, Henk Huijgen, Angelica Loning, Brian McSweeney, Math Verstraelen, Bang Pham, and Jeroen Kettenis. A video signal processor for motion-compensated field-rate upconversion in consumer television. *IEEE Journal of Solid-Sate Circuits*, 31(11):1762 – 1769, 1996.

- P.E.R. Lippens, J.L. van Meerbergen, A. van der Werf, W.F.J. Verhaegh, B.T. McSweeney, J.O. Huisken, and O.P. McArdle. PHIDEO: A silicon compiler for high speed algorithms. In *Proc. EDAC*, pages 436 441, 1991.

Nicholas Negroponte. Being Digital. Knopf, 1995.

- D.A. Patterson. Reduced instruction set computers. Comm. ACM, 28(1):8 21, 1985.

- Edwin Rijpkema, Gerben Hekstra, Ed Deprettere, and Ju Ma. A strategy for determining a Jacobi specific dataflow processor. In *Proceedings of 11th Int. Conference of Applications-specific Systems, Architectures and Processors (ASAP'97)*, pages 53 – 64, Zurich, Switzerland, 1997.

- Frank Rose. The end of TV as we know it. FORTUNE, pages 58 68, 1996.

- VHDL. *IEEE Standard VHDL Language Reference Manual*. IEEE Computer Service, 445 Hoes Lane, P.O. Box 1331, Piscataway, New Jersey, 08855-1331, 1993. IEEE Std 1076-1993.

- K.A. Vissers, G. Essink, P.H.J. van Gerwen, P.J.M. Janssen, O. Popp, E. Riddersma, and J.M. Veendrick. *Algorithms and Parallel VLSI Architectures III*, chapter Architecture and programming of two generations video signal processors, pages 167 – 178. Elsevier, 1995.

- John A. Watlington and V. Michael Bove Jr. Stream-based computing and future television. *SMPTE Journal*, 106(4):217 224, 1997.

## **Chapter 2**

## **Basic Definitions and Problem Statement**

#### Contents

| 2.1 | Stream | n-based Dataflow Architectures                    | 16 |

|-----|--------|---------------------------------------------------|----|

|     | 2.1.1  | Definitions                                       | 16 |

|     | 2.1.2  | Structure                                         | 19 |

|     | 2.1.3  | Behavior                                          | 22 |

| 2.2 | The C  | lass of Stream-based Dataflow Architectures       | 31 |

|     | 2.2.1  | Architecture Template                             | 32 |

|     | 2.2.2  | Design Space                                      | 32 |

| 2.3 | The D  | esigner's Problem                                 | 32 |

|     | 2.3.1  | Exploring the Design Space of Architectures       | 33 |

|     | 2.3.2  | Problems in Current Design Approaches             | 33 |

| 2.4 | Relate | ed Work on Dataflow Architectures                 | 34 |

|     | 2.4.1  | Implementation Problems of Dataflow Architectures | 35 |

|     | 2.4.2  | Other Dataflow Architectures                      | 35 |

|     | 2.4.3  | Implementing Stream-based Dataflow Architectures  | 36 |

| 2.5 | Concl  | usions                                            | 39 |

Showed that such architectures will be used for the high-performance video signal processing section in the TV-sets of the near future. In this chapter, we look in more detail at the structure and behavior of stream-based dataflow architectures.

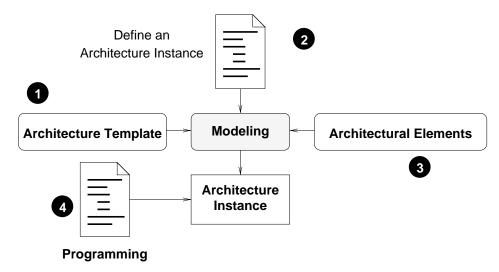

Stream-based dataflow architectures are not one particular architecture, but rather a class of architectures. This class is described using an architecture template to characterize the class in a parameterized form. The architecture template has an associated design space and the design of architectures becomes the selection of parameter values representing a particular architecture within the design space. The problem designers face, however, is how to select these parameter values. How do designers select these parameter values such that they result in architectures which satisfy the many design objectives involved, such as real-time constraints, throughput of the architecture and the efficiency of resources? At the same time, these architectures also need to be programmable enough that they can execute a set of applications.

We start in Section 2.1 by defining what a stream-based dataflow architecture is. We introduce definitions of terms to clarify what we understand in the context of this thesis by specific terms. We

also describe the structure and behavior of stream-based dataflow architectures and introduce the many choices present in both the structure and behavior of stream-based dataflow architectures. All these choices together characterize the class of stream-based dataflow architectures.

To describe the class of stream-based dataflow architectures, in Section 2.2 we introduce the architecture template, which characterizes this class of architectures in a parameterized form. By assigning values to all parameters in the architecture template, we can derive a particular architecture instance that makes up a design. This brings us in Section 2.3 to the goal of this thesis, which is to provide a systematic methodology for finding parameter values for an architecture template.

Dataflow architectures have already been around for many years in many different forms. We conclude this chapter in Section 2.4 by presenting related work on dataflow architectures. We identify known problems within dataflow architectures and indicate to what extent stream-based dataflow architectures exhibit these problems and how they cope with these problems.

### 2.1 Stream-based Dataflow Architectures

In the application domain of high performance real-time digital signal processing like video applications, the required processing power is in the order of hundreds of RISC-like operations per pixel, while data streams are in the range of 10 to 100 Msamples per second. Consequently, this kind of signal processing requires architectures that perform 10 to 100 billion operations per second and have an internal communication bandwidth of 1 - 10 Gbytes per second. By their nature, stream-based dataflow architectures comply with such requirements.

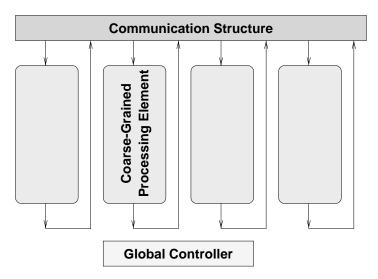

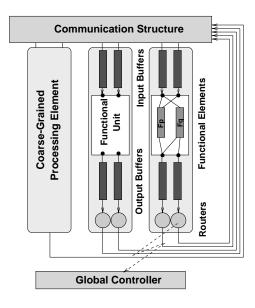

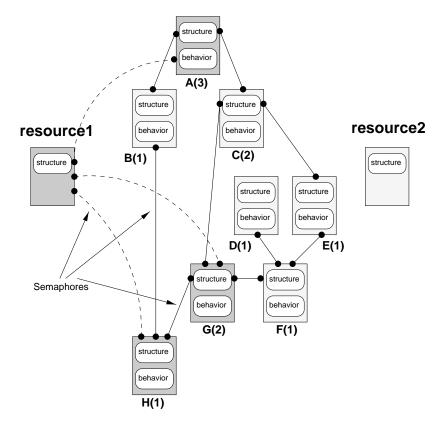

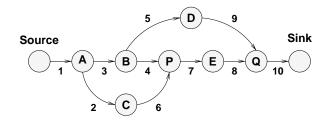

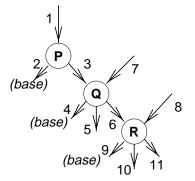

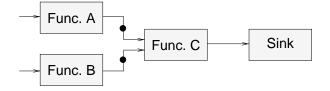

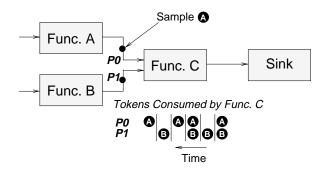

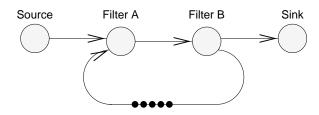

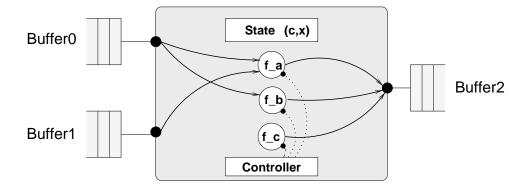

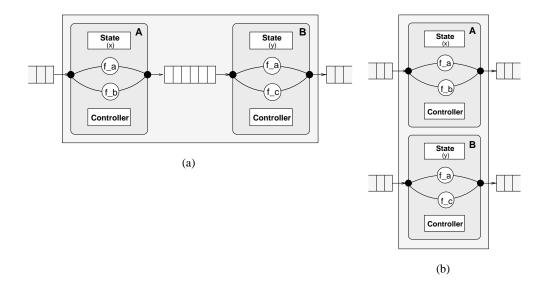

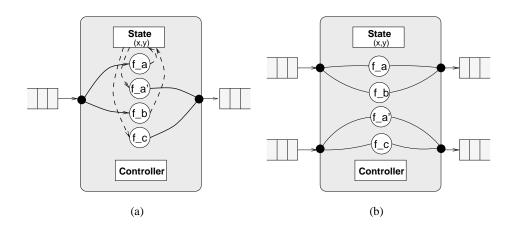

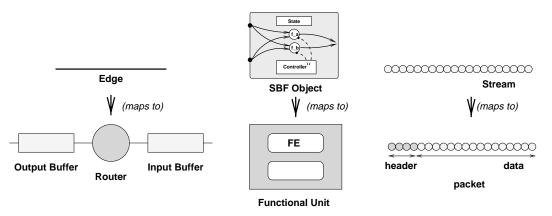

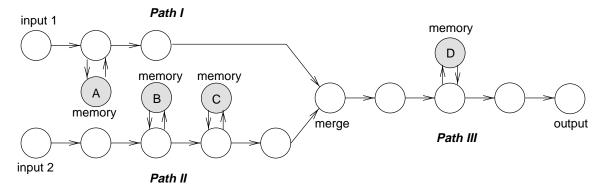

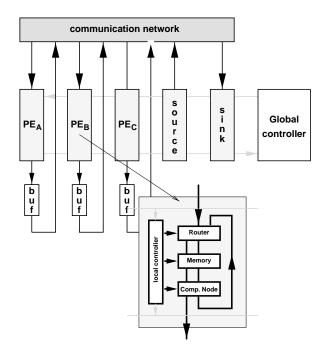

**Figure 2.1**. A stream-based dataflow architecture consisting of a number of *Processing Elements*, a *Communication Network*, and a *Global Controller*.

#### 2.1.1 Definitions

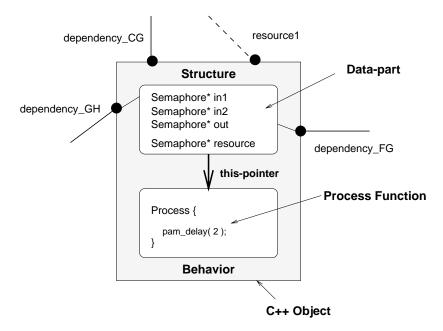

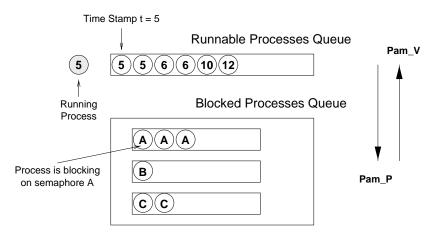

A schematic representation of the structure of a stream-based dataflow architecture is depicted in Figure 2.1. It consists of a number of *Processing Elements*, a *Communication Network*, and a *Global*

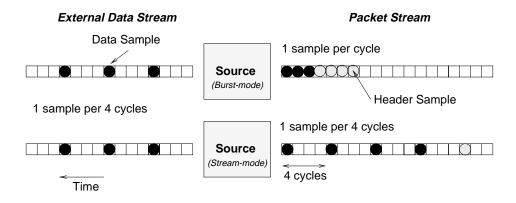

Controller. The processing elements operate concurrently on streams, which we define as

#### **Definition 2.1.** STREAM

A stream is a one-dimensional sequence of data items.

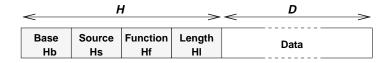

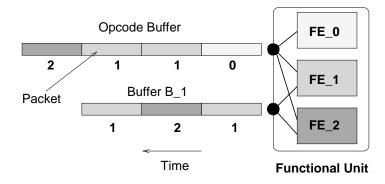

Unless stated differently, a data item represents a sample. In the case of video, a sample is typically a video pixel and in the case of radar, a sample is typically an integer or fixed-point value. A stream can be broken down into packets of finite length, resulting in a packet stream. We define a packet as

#### **Definition 2.2.** PACKET

A *packet* is a finite sequence of data items and is a concatenation of a header and a data part.  $\Box$

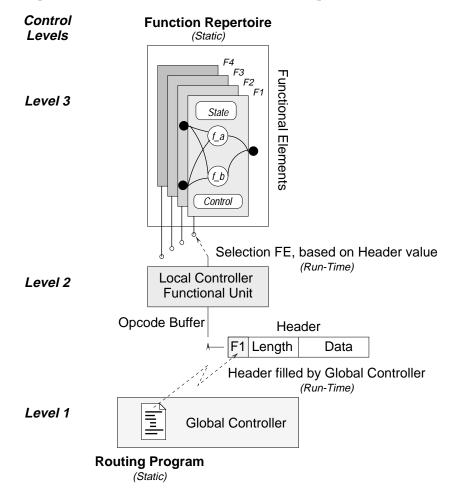

In the architecture, a processing element executes a pre-selected function operating on one or more streams and producing one or more output streams. The pre-selected function is one of a finite – typically, small – number of functions present in a processing element. These functions define the function repertoire of a processing element.

#### **Definition 2.3.** FUNCTION REPERTOIRE

The *function repertoire* of a processing element describes a finite number of different pre-defined functions that the processing element can execute.  $\Box$

Each processing element has a function repertoire that typically, but not necessarily, differs from the function repertoire of every other processing element. The grain sizes of the functions of the function repertoire are a measure of their complexity.

#### **Definition 2.4.** GRAIN SIZE

A function has a *grain size* expressed in terms of the equivalent number of representative RISC-like operations, like *Add*, *Compare*, and *Shift*. RISC-like functions have a grain size of one, by definition.  $\Box$

The grain size provides a metric allowing us to quantify the complexity of functions. A function with a grain size of 100 is supposed to have an executable specification in terms of approximately 100 RISC-like operations. [For more information on RISC instructions, see Appendix C of Hennessy and Patterson, 1996]. We say that functions with a grain size of one are *fine-grained*. Similarly, functions with a grain size between 1 and 10 are *medium-grained* functions, and functions with a grain size larger than 10 are *coarse-grained* functions.

Although processing elements execute in parallel, each and every processing element executes only one function from its function repertoire at a time. A processing element can switch at run-time between the functions of the function repertoire, which leads to the notion of weakly programmable processing elements.

#### Definition 2.5. WEAKLY PROGRAMMABLE PROCESSING ELEMENT

A weakly programmable processing element can switch at run-time between a fixed number of pre-defined functions present in the function repertoire in such a way that only one function of the function repertoire is active at a time.  $\Box$

Although the processing elements can execute functions ranging from fine-grained to coarsegrained, the functions that it executes are typically coarse-grained, to balance best between programmability and efficiency, as shown in Figure 1.4. When the granularity of functions increases, they become more dedicated and can, therefore, only be used to execute particular applications that

belong to a set of applications. Consequently, coarse-grained functions are more specific than finegrained functions used in fully programmable architectures. The weakly programmable processing elements and the grain size of the functions allow the architecture to provide just enough flexibility to support a set of applications. We assume that only one application is executed on the architecture at a time.

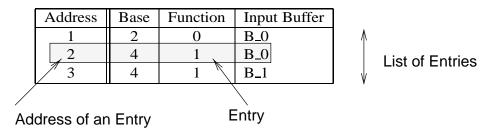

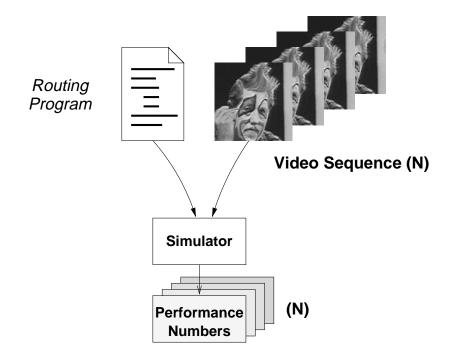

The global controller controls the flow of packets through the architecture. It contains a *Routing Program* with which to control the flow. This routing program indicates which processing element processes which stream, using which function from the function repertoire. By changing the routing program, we can *reprogram* the architecture to execute another application.

We define stream-based dataflow architectures as follows:

#### **Definition 2.6.** STREAM-BASED DATAFLOW ARCHITECTURES

A *Stream-based Dataflow Architecture* consists of a set of weakly programmable processing elements operating in parallel, a communication structure and a global controller. The processing elements operate on packet streams that they exchange among themselves via the communication structure controlled by the global controller.

Stream-based dataflow architectures have a particular hierarchical structure and a particular behavior in time. We will now describe the structure and behavior of the architecture in more detail, whereby we make use of the terminology that Veen [1986] uses to describe dataflow architectures in general.

We want to emphasize that the architecture concept shown in Figure 2.1 was proposed by Leijten, van Meerbergen, Timmer, and Jess [1997] and is further developed and discussed in greater detail in Leijten [1998].

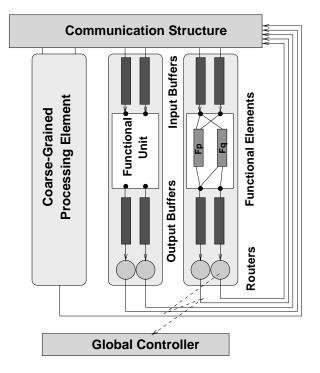

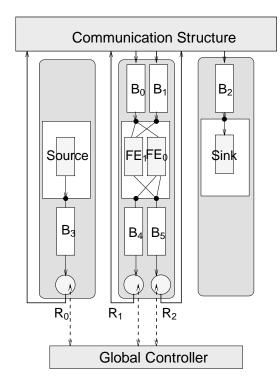

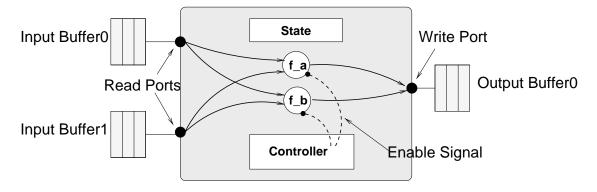

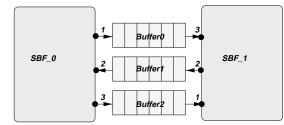

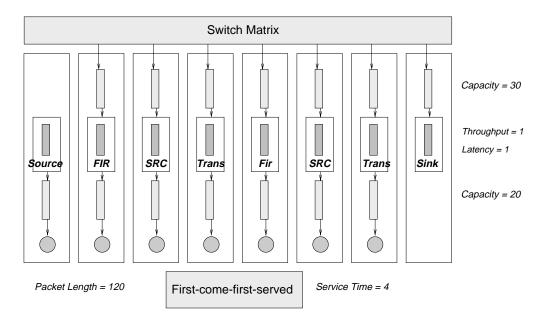

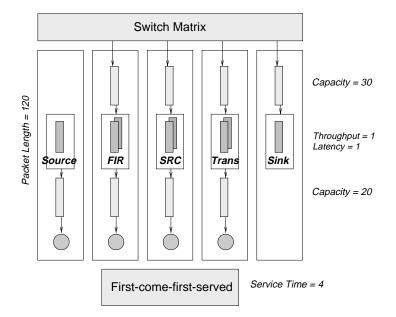

**Figure 2.2**. A detailed representation of the structure of a stream-based dataflow architecture. The architecture consists of a set of *processing elements*, a *communication structure*, and a *global controller*.

#### 2.1.2 Structure

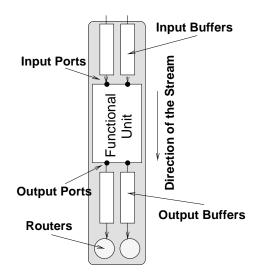

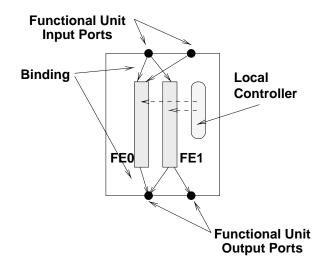

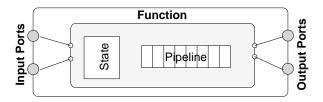

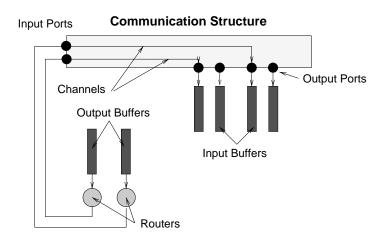

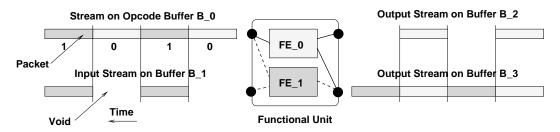

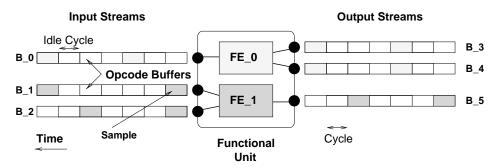

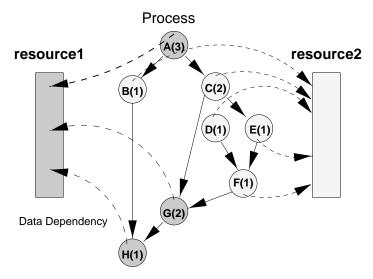

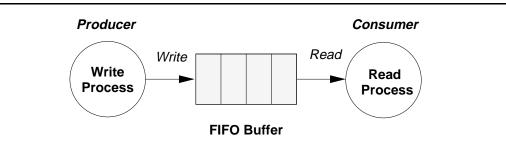

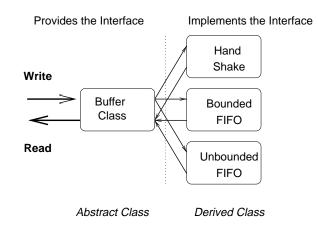

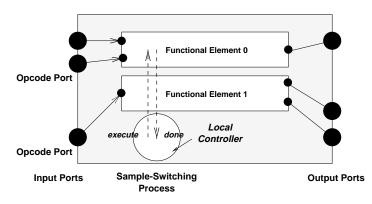

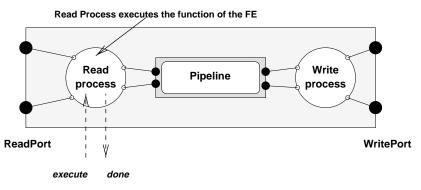

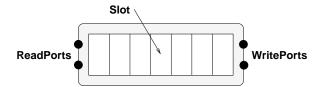

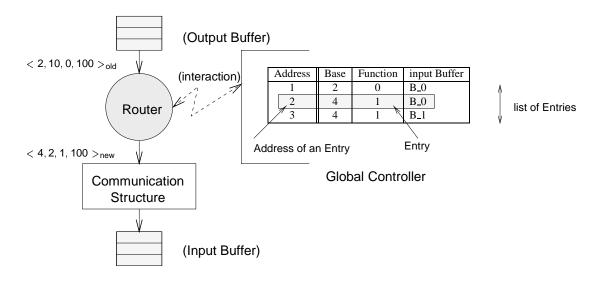

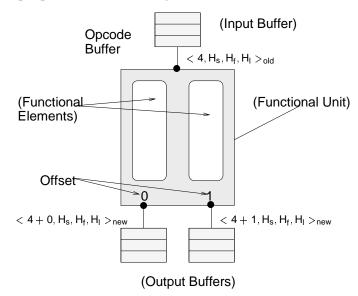

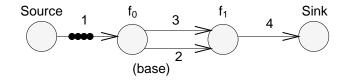

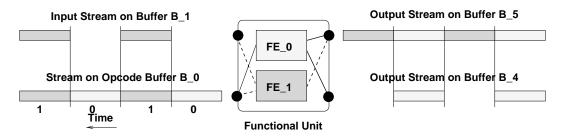

A stream-based dataflow architecture is given in Figure 2.2. The architecture consists of a set of *processing elements*, a *communication structure*, and a *global controller*. A processing element consists of a number of input and output *buffers* and *routers* and a *functional unit*. The routers interact with the global controller. The functional unit consists of a number of *functional elements* (i.e.,  $FE_p$  and  $FE_q$ ). Each functional element executes a function and the functions of the functional elements make up the function repertoire of a processing element. The communication structure interconnects the processing elements so they can communicate packet streams with each other under the control of the global controller.

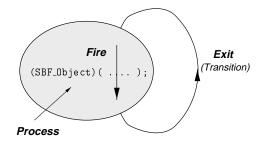

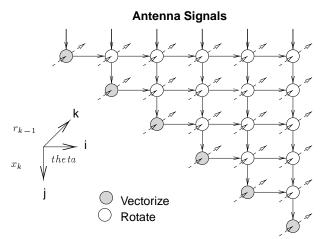

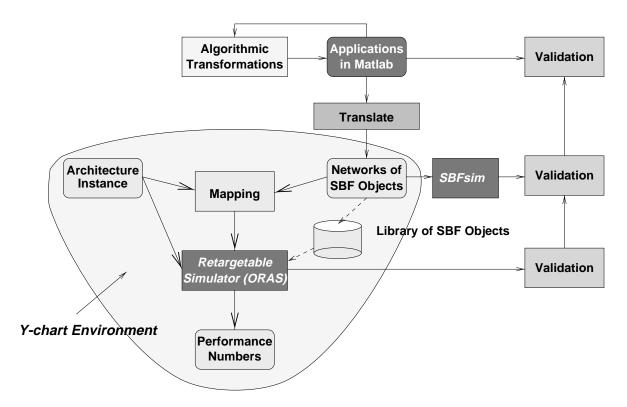

#### Packets