### Partial Evaluation for Code Generation from Domain-Specific Languages

Jia Zeng

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

### **COLUMBIA UNIVERSITY**

2007

©2007

Jia Zeng All Rights Reserved

### ABSTRACT

### Partial Evaluation for Code Generation from Domain-Specific Languages

### Jia Zeng

Partial evaluation has been applied to compiler optimization and generation for decades. Most of the successful partial evaluators have been designed for general-purpose languages. Our observation is that domain-specific languages are also suitable targets for partial evaluation. The unusual computational models in many DSLs bring challenges as well as optimization opportunities to the compiler.

To enable aggressive optimization, partial evaluation has to be specialized to fit the specific paradigm of a DSL. In this dissertation, we present three such specialized partial evaluation techniques designed for specific languages that address a variety of compilation concerns. The first algorithm provides a low-cost solution for simulating concurrency on a single-threaded processor. The second enables a compiler to compile modest-sized synchronous programs in pieces that involve communication cycles. The third statically elaborates recursive function calls that enable programmers to dynamically create a system's concurrent components in a convenient and algorithmic way. Our goal is to demonstrate the potential of partial evaluation to solve challenging issues in code generation for domain-specific languages.

Naturally, we do not cover all DSL compilation issues. We hope our work will enlighten and encourage future research on the application of partial evaluation to this area.

## Contents

| 1 | Intr | oductio  | n                                             | 1  |

|---|------|----------|-----------------------------------------------|----|

|   | 1.1  | Motiva   | ation and Purpose                             | 1  |

|   | 1.2  | A Brie   | of History of Partial Evaluation              | 3  |

|   | 1.3  | Outlin   | e of the Dissertation                         | 5  |

| 2 | Don  | nain Spo | ecific Languages                              | 8  |

|   | 2.1  | Detern   | ninistic Concurrent Languages                 | 11 |

|   |      | 2.1.1    | Esterel                                       | 11 |

|   |      | 2.1.2    | SHIM                                          | 14 |

|   |      | 2.1.3    | Bluespec                                      | 17 |

|   | 2.2  | A Littl  | le Language for Generating Dataflow Analyzers | 18 |

|   |      | 2.2.1    | Coding Dataflow Analysis Algorithms           | 19 |

|   |      | 2.2.2    | The Design of AG                              | 21 |

|   |      | 2.2.3    | Program Structure and Syntax                  | 22 |

|   |      | 2.2.4    | An Example                                    | 26 |

|   |      | 2.2.5    | Experimental Results                          | 30 |

|   |      | 2.2.6    | Related Work                                  | 32 |

|   |      | 2.2.7    | Conclusions                                   | 33 |

|   | 2.3  | Summ     | ary                                           | 35 |

| 3 | Part | ial Eva  | luation for Removing Concurrency              | 36 |

i

|                                                | 3.1  | Scheduling a Concurrent Program                | 37 |

|------------------------------------------------|------|------------------------------------------------|----|

|                                                |      | 3.1.1 The Program Dependence Graph             | 39 |

|                                                | 3.2  | Restructuring and Generating Code              | 41 |

|                                                |      | 3.2.1 Scheduling                               | 41 |

|                                                |      | 3.2.2 Restructuring the PDG                    | 46 |

|                                                |      | 3.2.3 Generating Sequential Code               | 55 |

|                                                | 3.3  | Experimental Results                           | 58 |

|                                                | 3.4  | Related Work                                   | 58 |

|                                                | 3.5  | Summary                                        | 60 |

| 4                                              | Part | tial Evaluation for Separate Compilation       | 62 |

|                                                | 4.1  | Compilation and Assembly of Concurrent Systems | 63 |

|                                                | 4.2  | The Graph Code Representation                  | 64 |

| 4.3 Generating Monotonic Three-Valued Programs |      | Generating Monotonic Three-Valued Programs     | 67 |

|                                                |      | 4.3.1 Adding Data Dependencies                 | 67 |

|                                                |      | 4.3.2 Summarizing Dependency Information       | 67 |

|                                                |      | 4.3.3 Construct                                | 69 |

|                                                |      | 4.3.4 State                                    | 71 |

|                                                |      | 4.3.5 Monotonicity                             | 71 |

|                                                |      | 4.3.6 The Example                              | 72 |

|                                                | 4.4  | Experimental Results                           | 73 |

|                                                | 4.5  | Related Work                                   | 74 |

|                                                | 4.6  | Summary                                        | 75 |

| 5                                              | Part | tial Evaluation for Unrolling Recursion        | 84 |

|                                                | 5.1  | Compilation of Recursive Programs              | 85 |

|                                                | 5.2  | Static Elaboration                             | 86 |

|                                                |      |                                                |    |

|                 | 5.3                                | Unrolling a Pipelined FIFO in SHIM                       | . 88  |

|-----------------|------------------------------------|----------------------------------------------------------|-------|

|                 | 5.4                                | Experimental Results                                     | . 94  |

|                 | 5.5                                | Related Work                                             | . 96  |

|                 | 5.6                                | Summary                                                  | . 98  |

| 6               | Con                                | clusions                                                 | 99    |

|                 | 6.1                                | Contributions                                            | . 99  |

|                 | 6.2                                | Future Work                                              | . 101 |

|                 |                                    | 6.2.1 Separate Compilation of Large Synchronous Programs | . 101 |

| Bibliography 10 |                                    |                                                          | 103   |

| A               | AG                                 | Syntax                                                   | 115   |

| B               | B Recursive FFT Example in SHIM 12 |                                                          |       |

# **List of Figures**

| 1.1                                                                         | An example in Java                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                                                                         | An example in Esterel                                                                                                                                                                                                                   |

| 2.2                                                                         | A simple example in SHIM                                                                                                                                                                                                                |

| 2.3                                                                         | An example in Bluespec                                                                                                                                                                                                                  |

| 2.4                                                                         | The operation of the AG framework                                                                                                                                                                                                       |

| 2.5                                                                         | The structure of an AG program                                                                                                                                                                                                          |

| 2.6                                                                         | A Complete AG analysis: Reaching Definitions                                                                                                                                                                                            |

| 2.7                                                                         | Part of the Phoenix (C++) code generated by the AG compiler for the                                                                                                                                                                     |

|                                                                             | reaching definitions example                                                                                                                                                                                                            |

|                                                                             |                                                                                                                                                                                                                                         |

| 3.1                                                                         | The Main procedure                                                                                                                                                                                                                      |

| 3.1<br>3.2                                                                  | The Main procedure.    39      A program dependence graph requiring interleaving.    41                                                                                                                                                 |

|                                                                             | -                                                                                                                                                                                                                                       |

| 3.2                                                                         | A program dependence graph requiring interleaving                                                                                                                                                                                       |

| 3.2<br>3.3                                                                  | A program dependence graph requiring interleaving.41Successor Priority Assignment.42                                                                                                                                                    |

| <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>                               | A program dependence graph requiring interleaving.       41         Successor Priority Assignment.       42         Priority Computation       44                                                                                       |

| <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul>                   | A program dependence graph requiring interleaving.       41         Successor Priority Assignment.       42         Priority Computation       44         The Scheduling Procedure       45                                             |

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul> | A program dependence graph requiring interleaving.       41         Successor Priority Assignment.       42         Priority Computation       44         The Scheduling Procedure       45         The Restructure procedure.       46 |

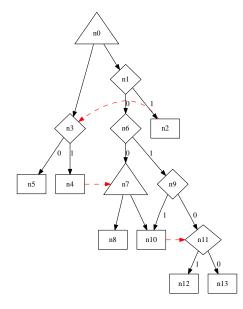

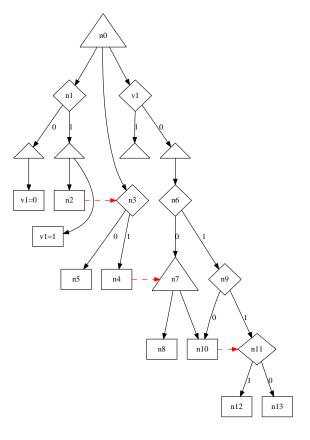

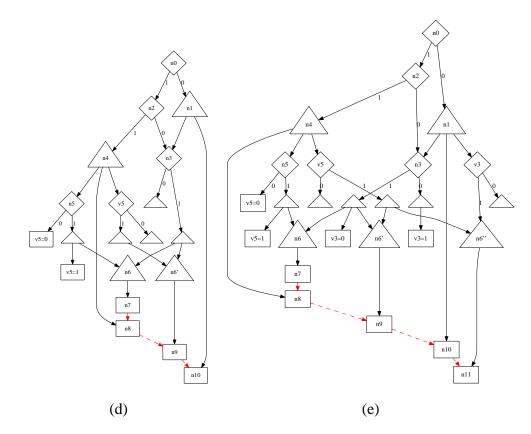

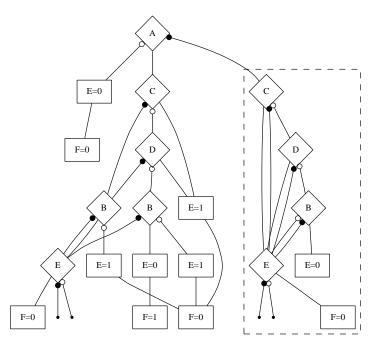

| 3.10 | The restructured PDG from Figure 3.2.                                    | 52  |

|------|--------------------------------------------------------------------------|-----|

| 3.11 | A complex example.                                                       | 53  |

| 3.12 | The reconstructed PDG from Figure 3.2 induced by a different schedule    | 55  |

| 3.13 | The PDG of Figure 3.12 after guard variable fusion                       | 56  |

| 3.14 | The successor ordering procedure                                         | 57  |

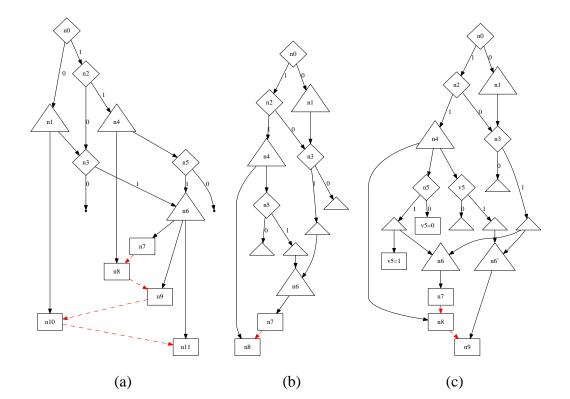

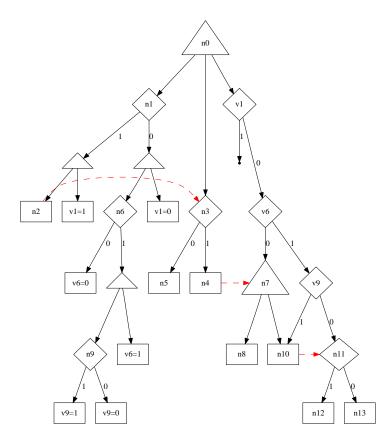

| 4.1  | A two-valued GRC before and after adding data dependence nodes and arcs. | 76  |

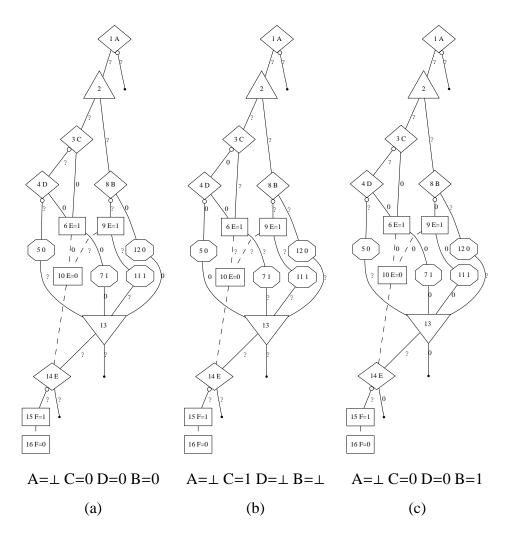

| 4.2  | Three-valued projection of the GRC in Figure 4.1(a)                      | 77  |

| 4.3  | The Main procedure                                                       | 77  |

| 4.4  | ComputeRelevantVars                                                      | 78  |

| 4.5  | The Construct Function                                                   | 79  |

| 4.6  | The MakeNode Function                                                    | 80  |

| 4.7  | The BuildCondition Function.                                             | 81  |

| 4.8  | (a) The BuildSync Function and (b) the PropagateZeros function           | 82  |

| 4.9  | Possible simulation states upon reaching node 14                         | 83  |

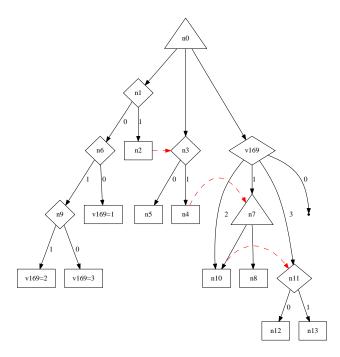

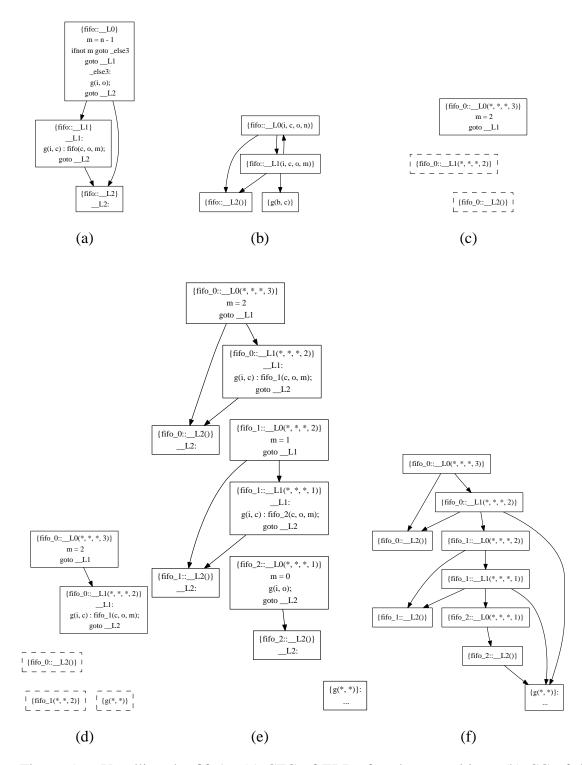

| 5.1  | The Main procedure.                                                      | 89  |

| 5.2  | The Unroll procedure                                                     | 90  |

| 5.3  | A FIFO program.                                                          | 91  |

| 5.4  | The FIFO after unrolling                                                 | 92  |

| 5.5  | The FIFO after inlining                                                  | 93  |

| 5.6  | Unrolling the fifo()                                                     | 95  |

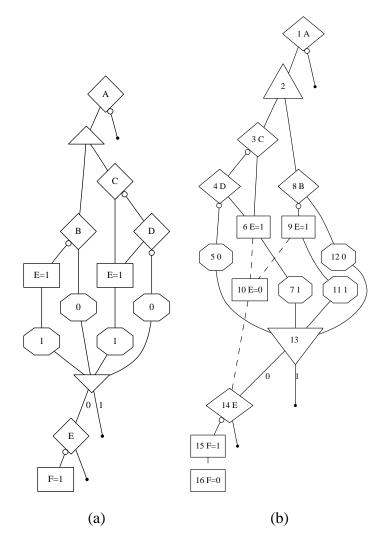

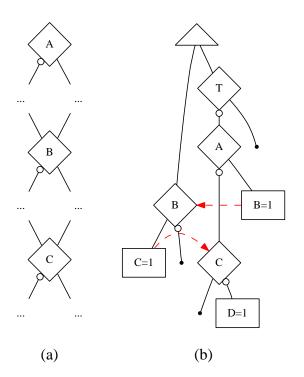

| 6.1  | Graph examples that may generate exponential code                        | 102 |

| 6.2  | The PDG transformed from Figure 6.1(a)                                   | 103 |

## **List of Tables**

| 2.1 | Comparing DSLs and GPLs | 10 |

|-----|-------------------------|----|

| 2.2 | AG Syntax Summary       | 25 |

| 2.3 | Experimental results    | 31 |

| 3.1 | Experimental Results    | 58 |

| 4.1 | Experimental Results    | 73 |

| 5.1 | Experimental Results    | 97 |

To my parents and my husband

## **Chapter 1**

## Introduction

### **1.1 Motivation and Purpose**

Partial evaluation (PE) optimizes programs by specialization. The idea is simple: consider the logic function  $(x \oplus y) \lor z$ . If y is always 1, we can simplify the function to  $\overline{x} \lor z$ . In other words, we customized a "y = 1" version of this function. To a partial evaluator resident in a compiler, the inputs used for specialization must be static. They can be some variables whose values are known, or even the structure of the program being compiled.

The main purpose of this dissertation is to demonstrate the potential of partial evaluation to solve challenging issues in compiling domain-specific languages (DSLs), which are designed to be used in specific fields of programming, such as Yacc for creating parsers and Verilog for designing hardware. To illustrate how to design an effective partial evaluation technique for a specific DSL, and we demonstrate three PE techniques that address various problems during code generation from DSLs.

By comparing DSLs to general-purpose languages (GPLs), we demonstrate some characteristics of DSLs that enable PE to work aggressively on DSLs. We compare different DSLs in the same domain, and we illustrate their special computational models and com-

| int i = 1;                                         | int i = 1;                              |

|----------------------------------------------------|-----------------------------------------|

| if (i > 0) {                                       | <pre>System.out.println("i = 1");</pre> |

| <pre>System.out.println("i = " + i);</pre>         |                                         |

| } else {                                           |                                         |

| <pre>System.err.println("Negative number!");</pre> |                                         |

| }                                                  |                                         |

Figure 1.1: An example in Java. (a) Original code. (b) After partial evaluation.

pilation challenges, which explain why it is necessary to design specific PE techniques for a DSL instead of using existing general partial evaluators.

Partial evaluation is well known for its application to compiler optimization and compiler generation. It is also referred to as *program specialization*. A specialized program usually runs faster than the original version since the partial evaluator may restructure the program's logic and carry out part of the computation at compile time. Figure 1.1 shows a print program in Java that can be simplified by partial evaluation. Nevertheless, the specialization process is nontrivial; it may change the semantics, cause an explosion in code size, or even may not terminate. For example, if in the Java example the variable *i*'s value relies on the input, the partial evaluator may explore all possible values of *i* and hence never terminate. Therefore, most PE techniques are conservative.

General PE techniques usually involve constant propagation, loop unrolling and inlining. Yet, PE is not just a collection of these techniques; it is combination of compilation techniques, language and semantics. Compared to constant propagation, which only deals with static values of variables, PE focuses on static "properties" of a program [26]. Therefore a PE system commonly performs in-depth flow analysis and requires comprehensive knowledge of semantics. For example, knowledge of data types and bounds on variable values, which are not helpful to constant propagation, may be used for program specialization, as Consel and Khoo show [26].

Our observation is that a domain-specific language, which has a simple but concise syntax, is a suitable target for applying partial evaluation. The simplified syntax eases the analysis workload of PE and enables PE to deeply understand the computational model underlying the program. Unfortunately, our survey of PE found no successful partial evaluator for DSLs, in part because most earlier work has focused on GPLs. Although some early work did apply PE to optimization or automatic compiler generation for DSLs, such techniques were too general to achieve any significant improvement. In contrast, PE in a restricted setting works more effectively for a specific paradigm. Each PE technique we demonstrate in this dissertation, for example, is carefully designed for the specific model of computation in the corresponding DSL. Each language's special features bring challenges as well as optimization opportunities to the compiler. Our experimental results show that PE is effective at addressing these challenges.

### **1.2 A Brief History of Partial Evaluation**

In 1952, Kleene [54] was the first to formulate partial evaluation (PE). His s-m-n theorem claims that, for an arbitrary function f with m + n arguments, when the values of the first m arguments are given, there always exists a specialized function g that takes the n arguments and behaves the same. More important, he proved there is a program to construct the specialized function. His theorem was later extended to improve a program's efficiency by specialization. Lombardi and Raphael, according to Jones [47], were the first to use the term "partial evaluation" in 1964 [45].

Most of the early work applied PE to compiling and compiler generation [43, 23, 6]. At that time, the most significant benefit that compilers gained from PE was not efficiency but automation. Based on the fact that a partial evaluator is a program by itself, Futamura [39] foresaw the self-application of PE, i.e., compiler generation. He did some experiments but never proved this idea. Proof would have to wait until 1985, when Jones et al. [46] created MIX, the first practical self-applicable partial evaluator for a language of first-order recursive equations. Later, more research was conducted on improving efficiency of compiled code generated by a partial evaluator, mainly by reducing the interpretive overhead added by the evaluator. Jørgensen [48], for example, managed to compile a lazy functional lan-

guage to generate code that runs faster than the commercial tool generated code does. The boom in research on PE in 1990's prompted the first PE conference in the US: the ACM SIGPLAN Symposium on Partial Evaluation and Semantics-Based Program Manipulation (PEPM).

Because of its conceptual simplicity and great automation, partial evaluation has been applied to many areas other than compilation, such as pattern matching, circuit simulation, numerical computations and computer graphics.

Traditional partial evaluators can be divided into two classes: online and offline. An online partial evaluator, which typically resides in the interpreter, relies on the concrete values computed at run time and makes decisions on the fly. Most of the early partial evaluators were online, which made them accurate but often very slow. To make specialization decisions at run time, an online partial evaluator usually embeds an interpreter in the generated program. Not being carefully optimized, this interpreter can cause an intolerable speed penalty.

An offline evaluator, in contrast, generates more general code since the program specialization relies on preprocessing results, not input values. It is usually separated into at least two stages. One is preprocessing, or binding-time analysis; the other is the specialization phase. The binding-time analyzer is responsible for collecting information, then determining whether the evaluation of an expression can be done at compile time or has to be deferred to run time. Later this information will be used to guide the specialization of the program [24]. All the PE techniques we introduce in later chapters are offline. Some partial evaluators aggressively combine these two methods to achieve best result [15], i.e., if an expression can be determined to be static at binding time, offline PE is applied, otherwise it is deferred to be treated by online PE at run time.

There are now many partial evaluators for general-purpose languages, such as C-Mix for C [40], JSpec for Java [65] and SML-mix for ML [13]. One of the most successful is Tempo, an offline C specializer developed in the Compose project at INRIA [25]. From a C program and an annotation of static inputs during specialization, Tempo performs a

sequence of analyses (alias analysis, side-effect analysis, binding time analysis, etc.) and preprocessing steps (goto elimination, function pointer elimination, etc.), then passes abstract code to specialization phases, which generate efficient code. Tempo has been applied to various domains, including operating systems, networking, graphics, etc., and proved effective. Also, some compilers for other languages [57], such as Java and C++, use Tempo as an optimizing back-end.

Although Tempo accepts most of ANSI C, there are still some complex features it cannot deal with, such as bit fields and mutually recursive structures. The alias analysis has some constraints also. These complex features of C limit the specializer's precision to some degree.

The interest in applying partial evaluation to domain-specific languages has grown in recent years. Burchett et al. [18] developed a partial evaluator that reduces the size of the dynamically changed graph size when programming in an interactive dataflow language. Edwards [33] demonstrated a program specialization that dramatically speeds up fixed-point simulation of signal processing kernels written in SystemC – another high-level hardware design language like those we compare in Chapter 2. These works reinforce our observation that partial evaluation can be very effective in optimizing DSLs.

### **1.3** Outline of the Dissertation

This dissertation is organized as follows:

Part I (Chapter 1) provided an overview of the dissertation as well as an introduction to partial evaluation. We first reviewed the basic concept of partial evaluation, its advantages and disadvantages for compilation application. To distinguish PE from traditional optimization techniques, we compared it to constant propagation as an example. The brief survey of partial evaluation in Section 1.2 introduced the origin of PE, its early applications, classification and the state of the art. We briefly explained our thesis statement that specialized PE is ideal for DSL compilation but left the details to following chapters.

#### CHAPTER 1. INTRODUCTION

Part II (Chapter 2) introduces the other important concept in this dissertation: domainspecific languages. The purpose of this part is to provide readers with some background knowledge of domain-specific languages and the compilation challenges they pose. We answer three questions here: why DSLs are useful in their domains, why partial evaluation can be effective for DSLs and why we must use specialized PE techniques instead of general ones to solve the problems of DSL compilation.

The answer to these questions motivates our consideration of DSLs in our research: a DSL, whose syntax is usually simpler than a GPL, relieves the compiler from complex semantic analyses but requires the partial evaluator resident in the compiler to understand its specific model deeply to achieve effective optimization results.

Part III (Chapter 3–Chapter 5) is our main technical contributions. We present three PE techniques for code generation that are applied to two concurrent, deterministic DSLs. These techniques remove concurrency (Chapter 3), enable separate compilation (Chapter 4) and unroll recursion (Chapter 5). Although the first two are for Esterel, a concurrent synchronous language, they approach the language differently. The specialization processes, therefore, are also different.

The algorithm described in Chapter 3 enables the efficient simulation of synchronous concurrent programs on a single-threaded processor. Synchronous languages, such as Esterel, provide embedded system designers a convenient tool that guarantees deterministic concurrency. However, it is nontrivial to statically schedule such a concurrent program running on a single-threaded processor. The data dependence among threads may cause frequent switches that bring considerable overhead. The solution we propose is to first eliminate as many control dependences in the program as possible, i.e., to break the source code into many small and concurrent pieces. The newly exposed concurrency, instead of introducing higher scheduling overhead as one would imagine, in fact provides the scheduler more choices and enables it to form larger and hence fewer atomic blocks. In this way, it minimizes switching overhead and generates much more efficient code.

The second algorithm we implemented for Esterel enables separately compiling code

segments of a synchronous design (Chapter 4). For a large design, it is normal to first code and test every module individually, then assemble them. However, if some modules form a communication cycle, the inputs that rely on other modules' outputs may not be available at run time to begin with. It would be very complex to write a program that handles all these cases explicitly. In this case, partial evaluation provides us an automatic way to infer the extra behavior. Performing an abstract three-valued simulation, the compiler generates descriptions that respond to unknown inputs. To keep the size of the generated code under control, we try to identify equivalent states during the simulation. The generated code, therefore, can tolerate unknown inputs and be compiled separately.

In Chapter 5, we present a PE technique that statically elaborates recursive function calls in SHIM programs. For a valid hardware design, it produces non-recursive code that is guaranteed to use bounded resources. Like Esterel, SHIM provides deterministic concurrency but presents it in an asynchronous model that uses rendezvous-style communication. Its recursive function calls enable users to construct concurrent structures dynamically. To make such programs predictable yet flexible, we use partial evaluation to eliminate recursion and replace it with static concurrent structures when possible. The algorithm applies customized constant propagation and function inlining to unroll cycles in the function call graph (recursive calls) as well as those in the control-flow graph (loops).

These various customized PE techniques illustrate the potential of partial evaluation to effectively solve compilation challenges of DSLs. They also show that aggressive optimization of a DSL requires a PE technique to be designed carefully to fit the specific model defined by the language's semantics.

### Chapter 2

## **Domain Specific Languages**

In this chapter, we introduce some domain-specific languages to illustrate the importance of DSLs and the challenges they present for compiler construction. Understanding these issues will help the reader to better appreciate the major technical contributions in the later chapters. We start with a special category, deterministic concurrent languages (Section 2.1), whose model has been used in hardware design for decades and which has also been gradually adapted to software design. Most of our research is based on these kinds of DSLs, especially on Esterel and SHIM, whose interesting models and challenging features inspired our work. We compare these two DSLs to Bluespec, another concurrent languages in the same application domain.

In Section 2.2, we present AG, a DSL of our own design. We include it to emphasize the importance and unique aspects (challenges) of DSLs, and to demonstrate how a DSL can facilitate the design of special-purpose systems (e.g., hardware circuit design, dataflow analysis, etc.). AG is designed to generate dataflow analyzers. We focused on making its syntax concise with an affordable performance penalty. At the end of Section 2.2, we introduce some related work and conclude.

Besides the languages' diversity, the comparison among the hardware design languages illustrates one of our hypotheses: specialized partial evaluation techniques rather than general ones are needed to achieve aggressive optimization for DSLs. Therefore, a deep understanding of a DSL's semantics is essential for developing effective PE techniques for it.

A domain-specific language is designed to serve a specific field of programming, such as Verilog for RTL (Register-Transfer Level) design, Matlab for math computation, HTML for web page description, etc. They are usually designed with some specific syntax constructs and combined with some built-in facilities that make the design work more convenient and efficient.

The diversity and sophistication of the engineering industry inspired the birth of DSLs. In addition, a well-developed DSL may even boost the prosperity of the related domain. Verilog [71], for example, enabled the automation of circuit design, which heavily depended on manual design before 1980s. Manual design was extremely time-consuming and tedious; every chip at that time could only contain hundreds of transistors. During 1980s, things changed with the automation of circuit design, which enabled the faster design of larger systems. Many languages and tools were developed specifically in this area at the same time. Verilog, which started as a simulation language to describe the algebra of digital logic computation [38], soon became popular both because of its flexible syntax for describing test benches and because of its integrated high-performance simulator. Later, Synopsys adopted Verilog for RTL logic synthesis. It has been very successful since then. Verilog helped users to better understand the behavior-level modeling of the circuit, which in fact sped up the automation process of hardware design. Now we are able to put millions of transistors on a chip, which would not have happened without the invention of Verilog. Verilog shows how a well-designed DSL can have a major beneficial impact on a discipline — in this case, hardware engineering.

Compared to a general-purpose language (GPL), a DSL usually has a simpler syntax designed to concisely fit the logic and behavioral model in its applied field. Table 2.1 summarizes the differences between DSLs and GPLs. For example, when modeling a control-dominated embedded system, which has to meet both hard time control and ef-

#### CHAPTER 2. DOMAIN SPECIFIC LANGUAGES

|                                 | DSLs        | GPLs    |

|---------------------------------|-------------|---------|

| concise syntax                  | very        | yes     |

| general application             | no          | yes     |

| specific model                  | yes         | no      |

| difficulty of semantic analysis | low         | high    |

| effective PE technique          | specialized | general |

Table 2.1: Comparing DSLs and GPLs

ficiency requirements, Esterel can provide a deterministic and concurrent solution that is more elegant and efficient than a C solution. GPLs are not an ideal solution in this specific domain because the designers' concerns are not well addressed by any GPL. Consider Java. Garbage collection, which has been welcomed by general users, turns out to be the reason that embedded system designers reject the language; losing control of memory makes them worry about unpredictable behavior occurring in a system.

The characteristics of DSLs listed in Table 2.1 relieve compilers from complex semantic analysis but place higher optimization requirements on these compilers. As we demonstrate in the next few chapters, partial evaluation does a good job of optimization. It can effectively improve the performance of the generated code. However, the various models of DSLs demand that specific partial evaluation techniques have to be designed for different models to achieve the best optimization result. The partial evaluation technique we introduce in Chapter 3, for example, works well on Esterel, but would not be helpful for VHDL. By analyzing the data and the control dependencies in Esterel programs, the compiler increases the degree of concurrency in the code and thus provides more flexibility to the optimization step that manages to generate efficient code. General PE techniques would not work well in this case since Esterel is a concurrent language and the primary performance penalty comes from context switching between threads. So we customized a graph transformation that was originally used for sequential program optimization rather than using general PE techniques. Moreover, we specialized the data dependency analysis for the synchronous communication model in Esterel. Our experimental results show a more than four-fold speedup over existing tools, much better than what general PE could achieve.

By comparing and analyzing different models, this chapter explains why the partial evaluation techniques described in following chapters need to be radically different.

### 2.1 Deterministic Concurrent Languages

From multithreaded programming to multi-core system design, concurrency has many applications. But many concurrent models do not guarantee determinism, i.e., a program may behave differently at different times, even for the same input. To address this concern, certain DSLs for hardware design define strict semantics to ensure both concurrency and determinism. Esterel, for example, allows concurrent threads to communicate through signals in a single clock cycle but in a strict manner, i.e., all readers must wait for other writers that set the signal's value. On the other hand, SHIM, which does not provide global variables, instead uses single-input channels for interprocess communication. Through these strict semantics, these DSLs provide ideal solutions for designs that demand determinism and high efficiency. Embedded system design, which is naturally described as a combination of concurrent processes and does not expect any indeterminate behavior, is a good example of where we need these deterministic concurrent DSLs.

### 2.1.1 Esterel

Designed by Berry in 1982, Esterel [11] is a synchronous, cycle-accurate parallel language that uses a strict communication pattern. Dedicated to reactive systems, it emphasizes that users can describe control concisely. An Esterel program consists of several modules, each of which has inputs and outputs. A module, as shown in Figure 2.1, may contain multiple threads, separated by double bars. They march in step to a global clock and communicate with each other using a disciplined mechanism. In each clock cycle, the

```

module example:

input A;

output B, C, D;

loop % Thread I

present B then

emit C

end present;

pause

end

Ш

loop % Thread II

present T else

present A then

emit B

else

present C else

emit D

end present;

end present;

end present;

pause

end

```

end module

### Figure 2.1: An example in Esterel

program computes its outputs and progresses to the next state based on its inputs and the previous state.

Signals carry and deliver the major information throughout the program by broadcasting. These signals can be classified into input, output and local signals. A module's interface, for example, is composed of input/output signals. Normally, a pure signal in Esterel carries either a present or an absent Boolean value; such a value for an input signal is determined by the environment. An output or local signal's value, by contrast, can be set by a statement. This value does not persist between cycles. Besides the values of present and absent, we will introduce the third possible value of a signal - unknown - in Chapter 4, which may occur when some input signals are intermediate outputs of other running modules.

The syntax of Esterel is not complicated. We show a small part of it in the example in Figure 2.1, which implements two synchronized threads. Every thread in the example is enclosed in an iterative *loop* statement that takes more than one cycle to complete because of the *pause* statement, which idles for a cycle. Esterel does not allow intra-cycle loops. The other statements, *present* and *emit*, execute within a cycle. The *present* keyword tests a given signal's value and *emit* sets a signal to present, respectively. Comments are denoted by %.

Despite its concise semantics, Esterel can be used to define quite complicated interactions between threads, which can make it hard to generate efficient code. To simulate concurrent threads on a single-threaded processor, threads may have to interleave during execution. Instead of shared memory or semaphores, threads in Esterel communicate through signals and follow the rule of reader-after-writer to ensure determinism. In Figure 2.1, for example, Thread I has to start running only after Thread II since Thread II may set signal B's value, which Thread I requests. However, the else branch of Thread II contains a present test on signal C. To acquire C's value, the program is forced to switch from Thread II to I. Such sequential ordering is not always so straightforward and may involve many possible choices during compilation. Therefore, minimizing the number of context switches becomes the key to boosting the performance of generated code.

The synchronous and imperative semantics of Esterel simplify programming but complicate code generation. Esterel requires any implementation to deal with three issues: the concurrent execution of sequential threads of control within a cycle, scheduling constraints among these threads due to communication dependencies, and how (control) state is updated between cycles. To solve these issues, many different techniques have been proposed. The Esterel V3 compiler translated programs to automata. This produces quite efficient code but the size of the generated code may be exponential. V5 avoided the scale problem by generating circuit-like code, but this turned out to be slow at run time. Later, Potop-Butucaru [63] created a new intermediate representation (IR) and optimizations that greatly improved the generated code. Based on this new IR and the work by Edwards [29], we developed a compiler that, by analyzing data and control dependencies in a program, makes aggressive optimizations and generates efficient and compact code.

### 2.1.2 SHIM

SHIM [32], invented by Edwards & Tardieu recently, provides a solution for designing heterogeneous embedded systems: systems combined of software and hardware. Software modules are commonly event-driven, flexible and fit well with the asynchronous model. SHIM takes the asynchronous approach where threads only synchronize with others when they must communicate.

In heterogeneous systems, especially when hardware and software have to communicate frequently, the SHIM model shows advantages over synchronous languages. The Robby Roto game, a traditional video game system, is a good example. The software typically runs at a frequency as low as 180 Hz, while the the hardware's frequency is 14 MHz - about 80,000 times faster. Obviously it would be more efficient to simulate these two at different clock frequencies and design an asynchronous interface for them. Flexibility is beneficial in these kinds of circumstances.

The syntax of SHIM is similar to C, but its use of concurrency and its rendezvous communication facility make it different. Figure 2.2 shows a sample program that deals with a sequence of integers. In this program, there's only one function main() that contains three threads where Thread II and III respectively receive even and odd numbers from Thread I. These threads are running concurrently, as the keyword *par* defines, and synchronize on channels *odd* and *n*. The *send* and *recv* statements indicate where a thread rendezvous on a channel. Unlike when a thread communicates through variables, a thread will block on a channel if its peer — another thread that communicates on the channel — is not ready. The *next* keyword represents *recv* when appears on the right side of an assignment and *send* when it appears on the left. In this program, *next odd* in Thread I means *send* since it sets *odd*'s value in the statement. The other two threads receive *odd*'s value. A channel

```

void main() {

int n = 0;

bool odd = 1;

try {

{

//Thread I

for (;;){

if (n < 10){

next odd = 1 - \text{odd};

send n;

n = n + 1;

}

else

throw T;

}

}

par

{

//Thread II

for (;;)

if (!(next odd))

recv n;

}

par

{

//Thread III

for (;;)

if (next odd)

recv n;

}

} catch(T) {}

}

```

Figure 2.2: A simple example in SHIM

must have exactly one sender but may have multiple receivers. This scheme makes the communication among concurrently running processes an arbitrary graph, which may be cyclic.

SHIM defines a complicated exception handling system that cooperates with concurrency. Generally speaking, a thread that communicates with any other thread will "die" if its peers are aborted. For example, Thread II (Figure 2.2), which contains an infinite *for* loop, seems to run forever. Nevertheless, when its peer Thread I throws an exception Tand terminates, Thread II will terminate as well, as will Thread III. This process is also called "poisoning" because it appears that the termination due to the exception is being propagated among threads through channels.

The computational model of SHIM is based on Kahn networks [49]. Although the scheduling-independent character of the model allows the compiler to make many scheduling choices, it is still hard to generate fast code from a SHIM program. One way to make the code run fast is to know at compile time when threads will rendezvous. In the example in Figure 2.2, Thread II will only retrieve the value from Thread I through channel *n* when the next integer is even. The process of actually determining when the threads will rendezvous, however, can become fairly involved. In addition, fanout and cyclic communication may further complicate the situation; because of these challenges, a compiler may have a difficult time statically scheduling the code. Furthermore, exception handling presents another challenge. Consider three threads A, B, and C (C contains both A and B: in other words, both A and B are child threads of C). Even if thread A raises an exception, thread C can potentially keep running because B may be unaffected by the exception from A. Tardieu and Edwards provided some rules to handle exceptions in their work [70].

Recursion in SHIM presents another challenge. SHIM provides recursive function calls to enable succinct designs. However, a design with recursive calls may need unbounded resources. This is unacceptable for hardware implementations, so it is sometimes necessary during the compilation process to eliminate recursion. We propose an algorithm to transform a program with recursion to one only requiring bounded resources when possible.

```

(* descending_urgency = ''proc2, proc1, proc0'' *)

rule proc0 (cond0);

x <= x + 1;

endrule

rule proc1 (cond1);

y <= x;

endrule

rule proc2 (cond2);

x <= x -1;

endrule</pre>

```

#### Figure 2.3: An example in Bluespec

More details are included in Chapter 5.

Although both SHIM and Esterel are concurrent, deterministic and modular, they address different concerns in embedded system designs. Esterel uses the synchronous model to provide precise control over system timing while SHIM uses the asynchronous model for flexibility.

### 2.1.3 Bluespec

Bluespec is another concurrent and deterministic tool for hardware design. It is based on Hoe and Arvind's 1999 proposal [44] of a synthesizable Term Rewriting Systems (TRS) model for microprocessor designs. The tool provides a lot of facilities, including optimizations, long-bit-vector support and verification. These facilities are attractive for high-level designs.

The language is called Bluespec Verilog (BSV) since its syntax is similar to Verilog but without the *always* keyword. Like other hardware design languages, it is strongly-typed and side-effect free. A BSV design is composed of modules. Each module includes a description of the system state elements, such as registers and atomic behavioral components (rules). The segment of BSV code in Figure 2.3 contains three rules and registers x and y.

Each rule's body describes the allowable sequence of state transitions and its head specifies the condition under which the rule is enabled. The rule *proc0*, for example, increases x's value when the Boolean condition *cond0* is satisfied. Although rules can involve complicated transitions, such as ones containing method calls, every rule is atomic, i.e., the specified state transition cannot be interrupted.

The main challenge for the BSV compiler is to build a run-time schedule that assures the atomicity constraints of the rules. Unlike Esterel and SHIM where a designer defines the control logic of the system, Bluespec has the compiler infer the optimal control structure from the rules. In other words, the TRS model implies what sequences of state transition are possible. Rules that do not modify the same state element may be scheduled to run concurrently. For example, the rules *proc0* and *proc1* have no conflict, so they can run in parallel if their conditions are true simultaneously. The rules *proc0* and *proc2*, on the other hand, both write to register *x*. When they are both enabled, the compiler has to check the priority specification, such as the first line in the example (Figure 2.3), or raise an error. Since a rule can invoke method calls, the state it reads or writes may be distributed across several modules. This makes the automatic generation of control logic even harder. Furthermore, any change in a module or its related modules must be verified to guarantee atomicity.

A smart schedule may lead the compiler to generate code as efficient as hand-coded Verilog [4], but heavy reliance on the compiler may raise concerns of losing control over the behavior of the system, especially for large designs.

### 2.2 A Little Language for Generating Dataflow Analyzers

To illustrate in detail how a domain-specific language can help to simplify the development process, we present a little language called Analyzer Generator in this section. The concise syntax of the language can greatly reduce code size. We also introduce some potential PE optimization opportunities provided by the language at the end of this section.

Dataflow analysis is a well-understood and very powerful technique for analyzing programs as part of the compilation process. Virtually all compilers use some sort of dataflow analysis as part of their optimization phase. However, despite being well-understood theoretically, such analyses are often difficult to code, making it difficult to quickly experiment with variants.

Our domain-specific language, Analyzer Generator (AG), synthesizes dataflow analysis phases for Microsoft's Phoenix compiler framework. AG hides the fussy details needed to make analyses modular, yet generates code that is as efficient as the hand-coded equivalent. One key construct we introduce allows IR object classes to be extended without recompiling.

Through AG, we demonstrate how necessary and helpful a DSL is when we design programs applied to a specific domain. Experimental results on three analyses show that AG code can be one-tenth the size of the equivalent handwritten C++ code with no loss of performance. It shows that AG can make developing new dataflow analyses much easier.

### 2.2.1 Coding Dataflow Analysis Algorithms

Modern optimizing compilers are sprawling beasts. GCC 4.0.2, for example, tips the scales at over a million lines of code. Much of its heft is due simply to its many features: complete support for a real-world language, a hundred or more optimization algorithms, and countless back-ends. But the intrinsic complexity of its internal structures' APIs and the verbosity of its implementation language are also significant contributors.

We address the latter problem by providing a domain-specific language, AG for "Analyzer Generator," for writing dataflow analysis phases in Microsoft's Phoenix compiler framework. Experimentally, we show functionally equivalent analyses coded in AG can be less than one-tenth the number of lines of their hand-coded C++ counterparts and have comparable performance.

Reducing the number of lines of code needed to describe a particular analysis can reduce both coding and debugging time. We expect our language will make it possible to quickly conduct experiments that compare the effectiveness of various analyses. Finally, by providing a concise language that allows analyses to be coded in a pseudo-code-like notation mimicking standard texts [1], compiler students will be able to more quickly code and experiment with such algorithms.

One contribution of our work is a mechanism for dynamically extending existing classes. In writing a dataflow analysis, it is typical to want to add new fields and methods to existing classes in the intermediate representation (IR) in the analysis. Such fields, however, are unneeded after the analysis is completed, so we would like to discard them. While inheritance makes it easy to create new classes, most object-oriented languages do not allow existing classes to be changed. The main difference is that we want existing code to generate objects from the new class, which it would not otherwise do.

The challenge of extending classes is an active area of research in the aspect-oriented programming community [52], but their solutions differ from ours. For example, the very successful AspectJ [51] language provides the intertype declarations that can add fields and methods to existing classes. Like ours, this technique allows new class fields and methods to be defined outside the main file for the class, it is a compile-time mechanism that actually changes the underlying class representation, requiring the original class and everything that depends on it to be recompiled. In AG, only the code that extends the class must be recompiled when new fields are added.

MultiJava [22] provides a mechanism that is able to extend existing classes without recompiling them, much like our own, but their mechanism only allows adding methods, not fields, to existing classes.

In AG, we provide a seamless mechanism for adding annotations to existing IR classes. In AG code, the user may access such added fields with the same simple syntax as for fields in the original class. Adding such fields does not require recompiling any code that uses the original classes.

We implemented our AG compiler on top of Microsoft's Phoenix, a framework for building compilers and tools for program analysis, optimization, and testing. Like the SUIF system [76], Phoenix was specifically designed to be extensible and provides the ability, for example, to attach new fields to core data types without having to recompile the core. Unfortunately, implementing such a facility in C++ (in which Phoenix is coded) has a cost both in the complexity of code that makes use of such a facility and in its execution speed. Experimentally, we find the execution speed penalty is less than factor of four and could be improved; unfortunately, the verbosity penalty of using such a facility in C++ appears to be about a factor of six. Reducing this is one of the main advantages of AG.

### 2.2.2 The Design of AG

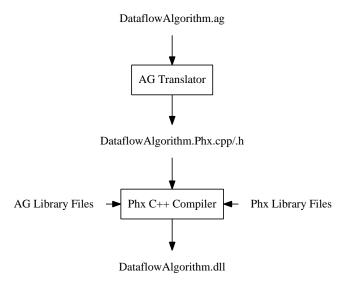

AG is a high-level language that provides abstractions to describe iterative dataflow analyses. The AG compiler translates an AG program into C++ source and header files, which are then compiled to produce a Dynamically Linked Library (DLL) file. (Figure 2.4) This DLL can then be plugged in to the Phoenix compiler and invoked just after a program is translated into Phoenix's Middle Intermediate Representation (MIR).

Our generated plug-in extends IR objects to collect information and invokes a traversal that is part of the Phoenix framework to perform iterative analysis. This traversal function invokes computations defined in the AG program.

We follow the classical dataflow analysis approach. An AG program implicitly traverses the control-flow graph of the program and considers a basic block at a time. Inside each block, the analysis manipulates its constituent instructions and operands. We thus chose to make blocks, instructions, and operands basic objects in AG. Phoenix, naturally, already has such data types, but AG makes them easier to uses since our language has a deeper understanding of them.

One of the main contributions of AG is the ability to add attributes and computations to these fundamental data types. This facility relies on mechanisms already built into Phoenix, but because of the limitations of C++, making use of such mechanisms is awkward and tedious to code. AG makes it much easier.

To simplify the description of computation functions, we included new statements in

Figure 2.4: The operation of the AG framework

AG such as *foreach* and data-flow equations like those found in any compiler text. We also introduced a *set* data type since data collected during dataflow analysis usually takes the form of sets.

AG relies on the Phoenix Traverser class. This is an iterative traverser that does not guarantee boundedness. See Nielson and Nielson [60] for a discussion of the issues in guaranteeing boundedness.

### 2.2.3 **Program Structure and Syntax**

The AG language is designed for dataflow analysis. It provides abstractions for the common features of iterative intraprocedural analysis. For user convenience and adaptability, we chose a syntax similar to that of C++ and added a variety of new statements and constructs.

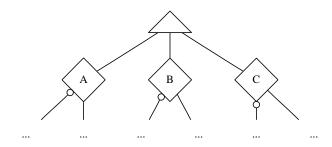

Figure 2.5 shows the structure of a typical AG program to describe an analyzer. It defines a new, named phase, extends a number of built-in Phoenix classes with new fields and methods to define what information to collect, and finally defines a transfer function for the dataflow analysis.

```

Phase name {

extend class name {

field declarations...

method declarations...

void Init() { . . . }

}

:

type TransFunc(direction) {

Compose(N) { . . . }

Meet(P) { . . . }

Result(N) { . . . }

}

}

```

Figure 2.5: The structure of an AG program

An *extend class* defines a new IR class that uses the Phoenix dynamically extensible IR class system. New fields and methods declared in an extend class are added as new class members. The user may directly refer to them as if they were members of the original class (our compiler identifies such fields and generates the appropriate Phoenix code to access and call members of such extended classes). Notice the methods declared in an extend class are "private," i.e., they can only be applied to the corresponding extend object, or in other methods declared under the same extend class. Currently, we only support extending Block, Instr, and Opnd classes.

In each extend class, the Init method behaves (and is executed as) an initializer just after the constructor for the extended class.

Each phase has a single TransFunc that defines the return type and iteration direction

(backward or forward) of the analyzer and, more importantly, the equations applied during the analysis. The body of a TransFunc may define functions, especially three reserved functions: Compose, Meet, and Result. Compose and Meet functions are applied when the traverser visits every blocks. The Compose function defines the computation inside a block using global data. The Meet function defines the computation performed between blocks, i.e., to merge data from the exit of the predecessor to the entry of the successor. The Result function defines operations to be performed just after the iteration. It usually propagates information to the objects that make up the blocks, such as instructions. Other functions may be declared in the TransFunc; they can be called by the three reserved functions or each other.

The user may embed arbitrary C++ code in the body of these methods. Such code segments are transparent to AG compiler, which simply includes them verbatim in the generated code.

We derived the syntax of AG from C++. We present its complete syntax in the appendix; Table 2.2 provides a summary. Below, we provide some details about its design.

Set is a data type similar to set in the C++ standard library. It can only apply to the reserved classes and actually refers to a set of IDs. For example, "Set<Instr>" will be translated into a bit-vector mapped on IDs of instructions in implementation. The *Map* type is similar.

During the analysis, the most relevant data are those with information for the entry and exit points of each block, so we introduced the *In* and *Out* data set as built-in variables.

Except for the two logical operators, the operators in Table 2.2 can be applied both to integers and *Set*-valued variables. Using the +, -, and \* operators generate code that perform Or, Minus, and And operations on bit vectors.

In dataflow analysis, one often needs to iterate over a subset of objects, so we added a *foreach* statement to do this. *Foreach* is a predicated iterator, meaning that it steps through the members of a set and performs actions on only selected members of the set. The user does not have to declare an iterator specifically, just a variable of the type over which the

| data types         | Set Map int bool void                                                        |

|--------------------|------------------------------------------------------------------------------|

| special variables  | In Out                                                                       |

| operators          | + - * = += -= *= &&                                                          |

| built-in classes   | Opnd Instr Block Alias Expr Func Region                                      |

| special methods    | Init Compose Meet Result                                                     |

| built-in functions | DstAliasTable SrcAliasTable Print                                            |

| built-in constants | Forward Backward                                                             |

| declarations       | Phase <i>identifier</i> ( <i>parameter list</i> ) { }                        |

|                    | extend class <i>type</i> { }                                                 |

|                    | type TransFunc ( direction ) { }                                             |

| statements         | <i>lvalue = expression</i> ;                                                 |

|                    | if ( <i>expression</i> ) { } else { }                                        |

|                    | /% arbitrary C++ code %/                                                     |

|                    | foreach ( <i>type var</i> in <i>range</i> where <i>cond. direction</i> ) { } |

|                    | <i>phoenix-iterator</i> ( ) { }                                              |

Table 2.2: AG Syntax Summary

iteration is occurring and the set on which to iterate. The user may also specify a condition that acts as a filter and a direction (Forward/increase or Backward/decrease). The condition is described with the *where* keyword. The syntax is shown in Table 2.2.

The *type*, *range* and *condition* allowed are listed in the attached syntax table. The "where *condition*" and "*direction*" parameters are optional.

Such *foreach* statements are translated to conditional for loops in the C++ and use the iterator macros in the Phoenix framework. Note that the *foreach* statement, especially the predication, is not strictly necessary (an additional *if* is sufficient), but the same can be said of C's *for* statement.

If the *range* is a Set, the *type* must match its content. Otherwise, if the *range* is a class, the *type* must match one of its members. For example, each instruction contains a list of

operands, so we can specify a *type* of Opnd and a *range* of an instruction. Also, the user may specify a *condition* of "dataflow && dst" to iterate over dataflow-related destination operands in the list.

Phoenix provides a number of iterator macros, which can be used in AG almost verbatim (see Figure 2.6 Line 9). The only difference is that in C++, a matching "next" macro must follow the use of each iterator macro (see Figure 2.7 Line 14); this is not necessary in AG.

*DstAliasTable* is a reserved function that takes an alias tag *x* as parameter and returns a set of destination operands whose alias-tag is *x*. Similarly, *SrcAliasTable* returns all source operands with the same alias-tag.

#### 2.2.4 An Example

To illustrate AG, we present a complete example: the classical "reaching definitions" analysis. The complete AG source is in Figure 2.6.

This algorithm computes the sets of definitions that reach the entry and exit points of each basic block in a program. Following the Dragon book [1], a definition of a variable is the operand in an instruction that may assign to the variable. In the Phoenix IR, each instruction has source operands and destination operands. For reaching definitions, we are concerned mostly with the destinations.

The whole analysis is defined as a phase called *ReachingDefs* (line 1 of Figure 2.6). The rest of the analysis consists of extend classes that add fields and computations to the built-in data types for operands, instructions, and basic blocks, and description of transfer functions.

*Extend classes* augment existing data types with additional fields in which to collect information and procedures for collecting it. This is similar to extending a base class in an object-oriented language, but differs because the new attributes are actually attached to objects of the "base class" itself at the language level, not just in objects of derived classes (the C++ code we generate from AG actually uses class inheritance). But a user can refer

```

1 Phase ReachingDefs {

extend class Opnd {

2

Set<Opnd> Gen;

3

Set<Opnd> Kill;

4

void Init() {

5

Opnd opnd = this;

6

if (opnd->IsDef) {

7

opnd->Gen += opnd;

8

foreach_must_total_alias_of_tag(alias_tag, opnd->AliasTag, AliasInfo)

9

opnd->Kill += DstAliasTable(alias_tag);

10

opnd->Kill -= opnd; }

11

}

12

}

13

14

extend class Instr {

15

Set<Opnd> Gen;

16

Set<Opnd> Kill;

17

void Init() {

18

Instr instr = this;

19

foreach (Opnd dstOpnd in instr where (dataflow && dst)) {

20

instr->Gen += dstOpnd->Gen;

21

instr->Kill += dstOpnd->Kill; }

22

}

23

}

24

25

extend class Block {

26

Set<Opnd> Gen;

27

Set<Opnd> Kill;

28

void Init() {

29

Block block = this;

30

foreach (Instr instr in block) {

31

block->Gen = instr->Gen + (block->Gen - instr->Kill);

32

block->Kill = block->Kill + instr->Kill - instr->Gen; }

33

}

34

}

35

36

Set<Opnd> TransFunc(Forward) {

37

Compose(N) { Out = In - N->Kill + N->Gen; }

38

Meet(P) { In += P->Out; }

39

40

}

41 }

```

```

1 class OpndExtensionObject : public Phx::RbagGenTest::AG::OpndExtensionObject {

PHX_DECLARE_PROPERTY(Phx::BitVector::Sparse *, Gen);

2

__PHX_DEFINED_VIRTUAL_GET_PROPERTY(Phx::BitVector::Sparse *, Gen) __const;

__PHX_DEFINED_VIRTUAL_SET_PROPERTY(Phx::BitVector::Sparse *, Gen);

Phx::BitVector::Sparse * _local_Gen;

5

6 }

7 void OpndExtensionObject::Init( Phx::FuncUnit *func_unit,

Phx::BitVector::Sparse *PHX_ARRAY(dst_alias_table)) {

8

Phx::IR::Opnd *opnd = _this;

9

if(opnd->IsDef) {

10

this->Gen->SetBit(this->uid);

11

foreach_must_total_alias_of_tag(alias_tag, opnd->AliasTag, func_unit->AliasInfo)

12

this->Kill->Or(dst_alias_table(alias_tag));

13

next_must_total_alias_of_tag;

14

this->Kill->ClearBit(this->uid);

15

16

}

17 }

18 void IterateData::Merge(Phx::DataFlow::Data *dependent_block_data,

Phx::DataFlow::Data *effected_block_data, Phx::DataFlow::MergeFlags flags) {

19

IterateData * dep_block_data = PTR_CAST(IterateData *, dependent_block_data);

20

Phx::BitVector::Sparse * Out = dep_block_data->Out;

21

if(flags & Phx::DataFlow::MergeFlags::First) In = Out->Copy(); else In->Or(Out);

22

23

dep_block_data->Out = Out;

24 }

25 void Traverser::InitData(Phx::BitVector::Sparse *PHX_ARRAY(dst_alias_table)) {

foreach_block_in_func(block, funcUnit) {

26

foreach_instr_in_block(instr, block) {

27

foreach_dataflow_dst_opnd(dstopnd, instr) {

28

OpndExtensionObject *ext_dstopnd = OpndExtensionObject::GetExtensionObject(dstopnd);

29

ext_dstopnd->Init(funcUnit, dst_alias_table);

30

} next_dataflow_dst_opnd;

31

InstrExtensionObject *ext_instr = InstrExtensionObject::GetExtensionObject(instr);

32

ext_instr->Init(funcUnit->Lifetime);

33

} next_instr_in_block;

34

BlockExtensionObject *ext_block = BlockExtensionObject::GetExtensionObject(block);

35

ext_block->Init(funcUnit->Lifetime);

36

} next_block_in_func;

37

38 }

```

Figure 2.7: Part of the Phoenix (C++) code generated by the AG compiler for the reaching definitions example

to new attributes as if they were already in the original class. Consider the Opnd extend class (lines 2-13). This adds two attributes to each operand, operand sets named *Gen* and *Kill*. As usual, the *Gen* set contains operands that are defined within the block and available immediately after it in the source code.

The *Init* function initializes the values of the *Gen* and *Kill* fields. The two sets are implemented as bit vectors—see Lines 2–5 in Figure 2.7 for the declaration of *Gen*; Lines 7–17 show the translation of the *Init* function. The body of *Init* adds destination operands to the *Gen* set. Similarly, all other destination operands in the built-in destination-opnd-map-to-alias-tag table (DstAliasTable) that have the same alias tag as the operand (i.e., when both modify the same memory location) are added to the *Kill* set (Lines 7–11).

The *Instr* and *Block* extend classes add *Gen* and *Kill* sets to each of their classes and populate these sets with data from *Opnd* and *Instr* objects respectively. Lines 26–37 in Figure 2.7 call the three *Init* functions (the translation of the other two are not shown). Note that this function is synthesized completely from how this data is used in the analyzer, not from explicit code in the AG source.

After collecting *Gen* and *Kill* sets for blocks, the algorithm specifies some details of the main analysis iteration. At the beginning of the transfer function *TransFunc*, the iteration is declared to proceed in the forward direction and return a set of *Opnd* objects.

The extend classes are based on original IR classes. The example in Figure 2.6 shows that, to refer to fields from the extend class (e.g., Figure 2.6, Line 8, "opnd->Gen"), the user may use the same notation as for those in the base class (e.g., Figure 2.6, Line 9: "opnd->AliasTag"). These two references generate very different C++ code (c.f. Figure 2.7, Lines 11 and 12).

As usual, we assume there are unique entry and exit points in the control flow graph for each block. "In" and "Out" are two built-in data sets related to the entry and the exit points respectively. The definition for TransFunc head declares the type of "In" and "Out" sets as holding operands. These two sets are usually used in the transfer function to pass data.

Compose and Meet are the two main functions for defining the transfer function. In

this program, they specify the two groups of dataflow equations in the standard way [1, Eq. 10.9]:

$$in[B_i] = \bigcup_{B_j \text{ a predecessor of } B_i} out[B_j]$$

$$out[B_i] = gen[B_i] \cup (in[B_i] - kill[B_i])$$

The first equation is exactly and simply included in the Meet function (Line 39), which computes the effect of the exit-point data from predecessors to the entry-point data of the current block in the iteration. *In* is related to the current block being visited, while *Out* is related to the block *P* that is passed to the *Meet* function. By default, the argument for the *Meet* function is a basic block that represents an arbitrary predecessor of the current block. As shown in Figure 2.7 lines 18–24, the data equation is translated into bit-vector manipulations.

The second dataflow equation is included in the *Compose* function (Line 38), which computes the data transformation globally from the entry point to the exit point for a single block. Declared as an argument to the *Compose* function, variable *N* is an extended object of the block by default. Since *Gen* and *Kill* are fields that have been added to the Block class (lines 27 and 28), they can be referred to as members of *N*.

A complete AG program is translated into a C++ program that is compiled as a plugin phase that can be invoked as part of the Phoenix compilation processes. It initializes all extended objects first, then executes the forward traverser, which applies the dataflow equations to iteratively compute on the blocks following the structure of the control-flow graph until the *In* sets converge for every block. The generated code uses the machinery built into the Phoenix framework to do this; an AG user does not write code for this.

## 2.2.5 Experimental Results

We tested AG on three analyses: reaching definitions, live variables, and uninitialized variables. We chose these three examples because a hand-written version of each, done by experienced programmers, already existed in Phoenix. We compared the size and speed of

|                     | Reaching Live |           | Uninitialized |  |

|---------------------|---------------|-----------|---------------|--|

|                     | Definitions   | Variables | Variables     |  |

| C++ LOC (manual)    | 791           | 303*      | 108†          |  |

| AG LOC (manual)     | 41            | 55        | 94            |  |

| C++ LOC (generated) | 626           | 519       | 682           |  |

| C++ runtime         | 7.3s          | 0.8s      | Ť             |  |

| AG runtime          | 7.4s          | 3.1s      | 13.6s         |  |

Table 2.3: Experimental results: size and speed of AG-generated code vs. handwritten. \*The manually coded live variable analysis uses hard-coded fields, which makes it simpler at the expense of being far less modular.

<sup>†</sup>The manually coded uninitialized variables analysis relies on the Phoenix SSA library not included in this count. This is a very different architecture than the code generated by AG.

the generated code with the manually written version for the first two examples because, like our generated code, they use the Traverser class in Phoenix. The manually written version of uninitialized variables used Phoenix's static single-assignment code, which AG does not take advantage of, so we did not experiment with it.

Table 2.3 shows our results. "LOC" indicates the number of lines of code excluding comments; times are in seconds. We computed the average run times of these plug-ins by running compiler with the plug-in, running the compiler without the plug-in, and subtracting these two running times. The times are thus a little suspect because they also include the time to load and initialize the plug-in itself.

In each test case, the C++ code generated by the AG compiler is more than six times the size of the AG source. Even better for AG, the manually written code for reaching definitions is even larger than the generated code. That is because the AG library files include commonly used code and default methods, for example, the constructor of the phase.

The manually written live-variables code is smaller than the generated C++ code for

that analysis, but this is because the manually written code does not use the (verbose) Phoenix extend objects.

We ran the generated Phoenix C++ code on a laptop with a 2.0 GHz Pentium-M processor running Windows XP. The benchmark is the Phoenix Microsoft Intermediate Language reader, which can generate high-level intermediate representations for a variety of targets. It is about five hundred thousand lines of code.

The AG-generated code for the reaching definitions analysis runs just as fast as the manually written code on the MSIL reader. Unfortunately, the live variable analysis code runs about one-fourth as quickly, but there is a good reason for this: the manually written C++ version does not use the Phoenix object-extension facility. Instead, it simply recomputes the desired data every time it traverses a block. Thus, the speed difference here more illustrates the cost of using extension objects instead a more brute-force approach. Evidently in this example, the computation is cheap enough so that repeating it is less costly than saving and recovering it later. We include the runtime for the AG code for uninitialized variables, but do not give a time for the manually written code because it uses a completely different algorithm.

## 2.2.6 Related Work