## **Precision Timed Infrastructure:** Languages, Compilers, and Hardware with **Ubiquitous Notion of Time**

June 28, 2013

### **David Broman**

broman@eecs.berkeley.edu

**EECS** Department University of California, Berkeley, USA and Linköping University, Sweden

### **PRET Infrastructure at Berkeley**

Jian Cai Hokeun Kim

David Broman Edward A. Lee Aviral Shrivastava Chris Shaver Yooseong Kim Michael Zimmer

# Agenda

broman@eecs.berkeley.edu

2

Part I Cyber-Physical Systems

Part II **Precision Timed** Infrastructure

3

# Part I Cyber-Physical Systems

Part I Cyber-Physical Systems Part II Precision Timed Infrastructure Part III Design Challenges

# **Cyber-Physical Systems (CPS)**

broman@eecs.berkeley.edu

4

Industrial Robots

### **Power Plants**

Aircraft

Part II Precision Timed Infrastructure

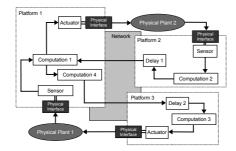

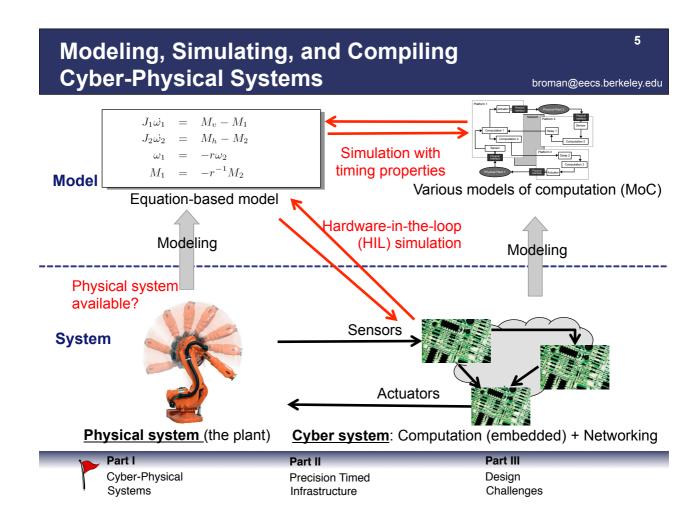

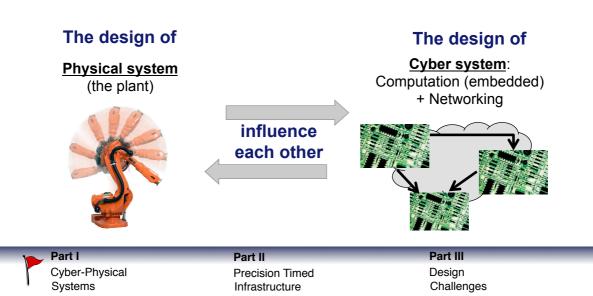

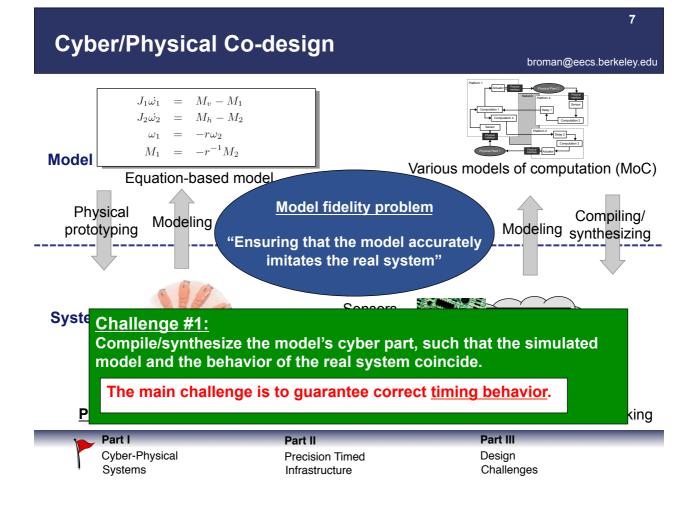

## **Cyber-Physical Co-Design Problem**

broman@eecs.berkeley.edu

6

Rapid development of CPS with high confidence of correctness is a <u>co-design problem</u>

# Part II Precision Timed Infrastructure

Part I Cyber-Physical Systems Part II Precision Timed Infrastructure

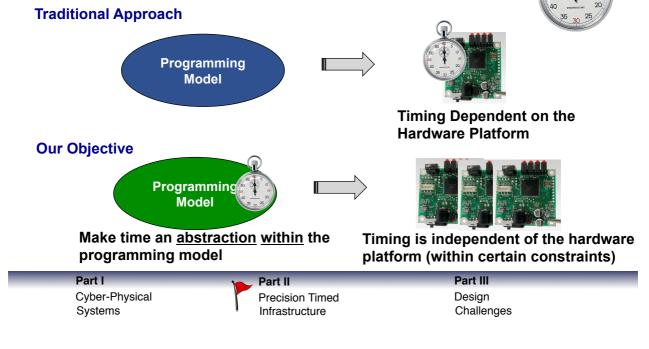

# **Programming Model and Time**

## Timing is not part of the software semantics

<u>Correct execution</u> of programs (e.g., in C, C++, C#, Java, Scala, Haskell, OCaml) has nothing to do with how long time things takes to execute.

# What is PRET?

| u        |

|----------|

|          |

|          |

| <u>и</u> |

| Ч        |

|          |

10

## **PRET = PRE**cision-Timed

Stephen Edwards and Edward A. Lee, "The Case for the Precision Timed (PRET) Machine", DAC, 2007

## **PRET Infrastructure**

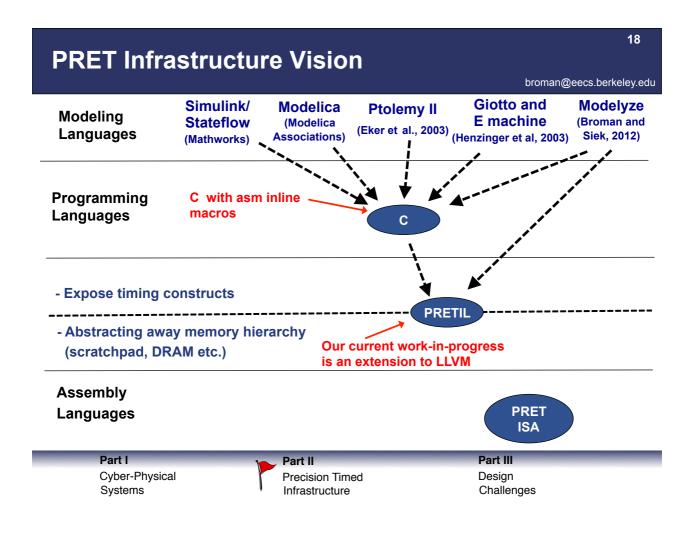

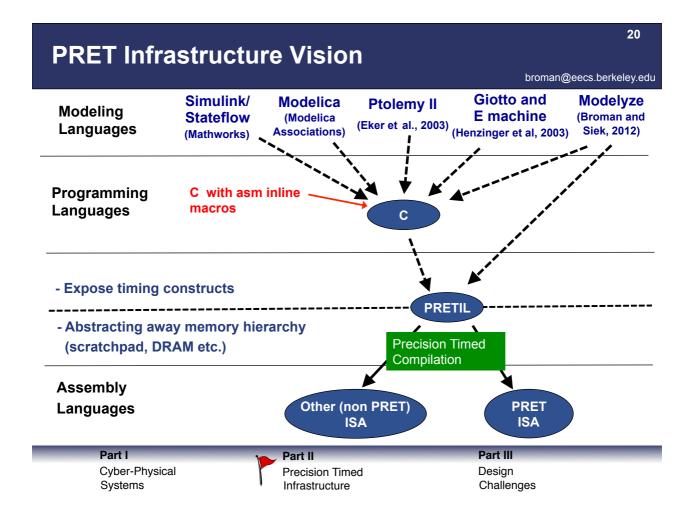

- PRET Language (Language with timing semantics)

- PRET Compiler (Timing aware compilation)

- **PRET Hardware (Computer Architecture)**

Part I Cyber-Physical Systems Part II Precision Timed Infrastructure Part III Design Challenges

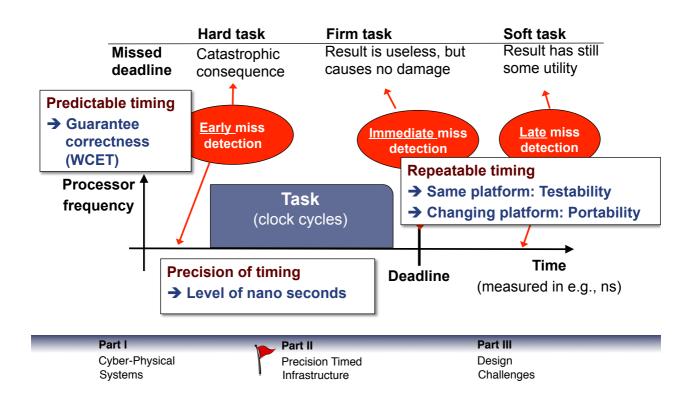

# **Detecting missed deadlines**

# What is our goal?

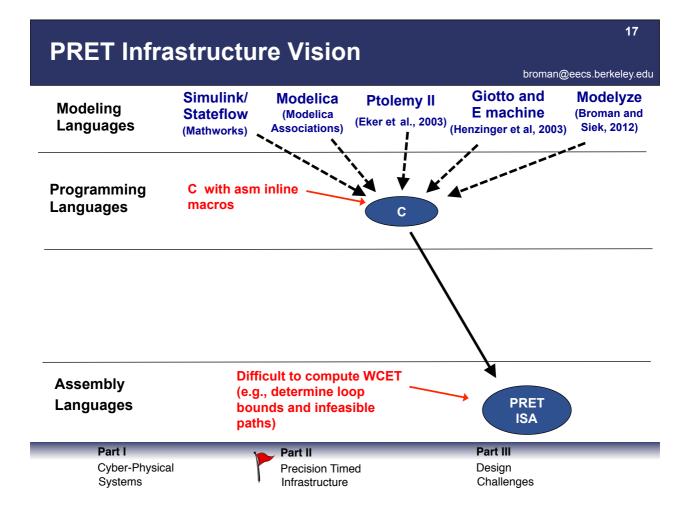

| Modeling<br>Languages    | Simulink/<br>Stateflow<br>(Mathworks)                    | Modelica<br>(Modelica<br>Associations)       | Ptolemy II<br>(Eker et al., 2003) | Modelyze<br>(Broman and<br>Siek, 2012) |  |  |

|--------------------------|----------------------------------------------------------|----------------------------------------------|-----------------------------------|----------------------------------------|--|--|

| Programming<br>Languages | Real-time Concurrent C<br>(Gehani and Ramamritham, 1991) |                                              |                                   |                                        |  |  |

|                          | Real-Tim<br>(Klingerma                                   | n <mark>e Euclid</mark><br>n & Stoyenko, 198 | 36)                               |                                        |  |  |

# The assembly languages for todays processors lack the notion of time

Part I Cyber-Physical Systems Part II Precision Timed Infrastructure Part III Design Challenges 14

## Instruction set architecture (ISA)

#### broman@eecs.berkeley.edu

### The good news

Fortunately, electronics technology delivers highly reliable and precise timing

### The bad news...

The chip architectures introduces highly non-deterministic behavior (e.g., using caches, pipelines etc.).

**Rethink the ISA** Timing has to be a *correctness* property not only a *performance* (quality) property

Photo by Andrew Dunn, 2005

16

broman@eecs.berkeley.edu

### **PRET Machine**

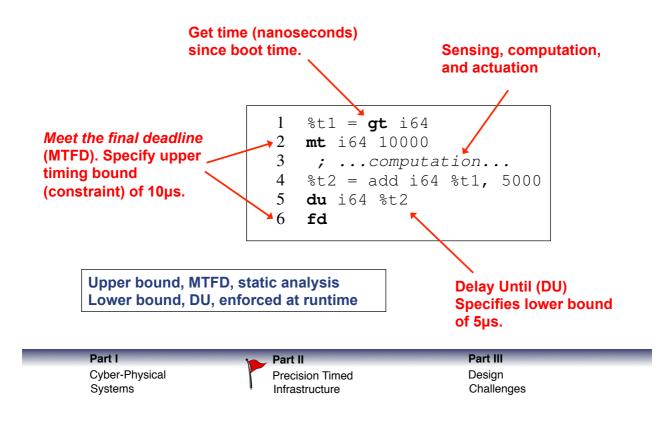

- Repeatable and predictable execution time (instructions)

- Repeatable memory access time

- Timing instructions for handling missed deadline detection

Part I Cyber-Physical Systems

| 1 | Faitin                 |

|---|------------------------|

|   | <b>Precision Timed</b> |

|   | Infrastructure         |

Design Challenges

Part III

# **Precision Timed Machine**

# PTARM (ICCD'12)

- Replacing caches with scratchpads

- Use a thread- interleaved pipeline (4 threads)

- Timing instructions (delay until, exceptionon-expire)

- Soft core on a Xilinx Virtex 5 FPGA

### FlexPRET (work-in-progress)

- Dynamically change no of active threads (1-8)

- RISC-V ISA (Waterman, Lee, Patterson, Asanovi, 2011)

| Java Optimized Processor (JOP)<br>(Schoeberl, 2008) | ARPRET<br>(Andalam et al., 2009) | Patmos<br>(Shoeberl et al) | XMOS<br>(May 2009) |  |

|-----------------------------------------------------|----------------------------------|----------------------------|--------------------|--|

| Part I                                              | Part II                          | Part III                   | _                  |  |

| Cyber-Physical                                      | Precision Timed                  | Design                     |                    |  |

| Systems                                             | Infrastructure                   | Challenges                 |                    |  |

# Intermediate Language (ptLLVM) example

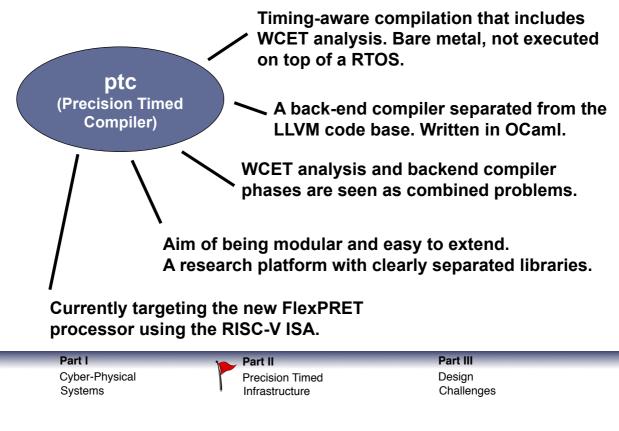

## Precision Timed Compiler (work-in-progress)

22 broman@eecs.berkeley.edu

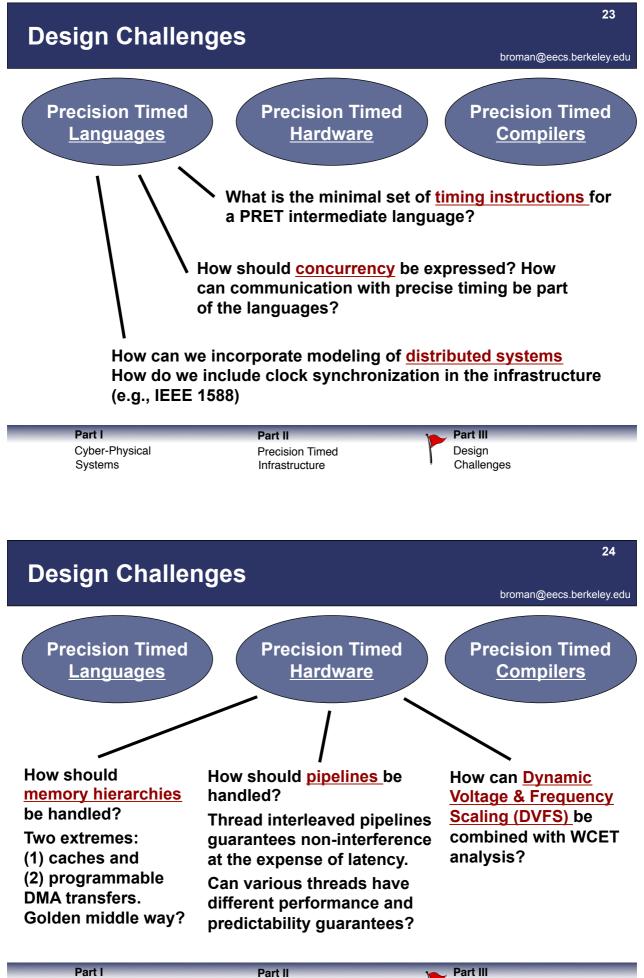

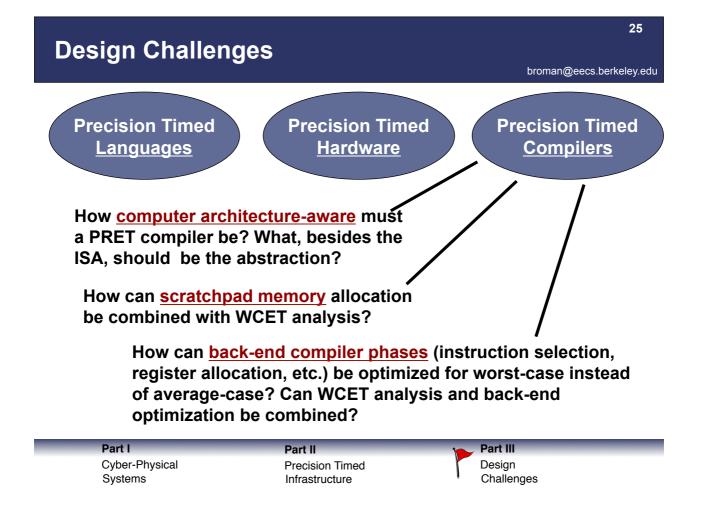

# Part III Design Challenges

Part I Cyber-Physical Systems Part II Precision Timed Infrastructure

Cyber-Physical Systems

Precision Timed Infrastructure Design Challenges

# Conclusions

### Main takeaway points

For CPS applications, time is a <u>correctness</u> <u>factor</u> – not just a performance (quality) factor

A <u>PRET intermediate language</u> language include timing semantics and abstracts away platform details.

<u>PRET Hardware</u> should give predictable timing behavior and provide hardware support for programming with real-time.

A <u>PRET compiler</u> should guarantee that all timing constraints are fulfilled when executed on a specific platform.

For more information see: http://chess.eecs.berkeley.edu/pret/

Thank you for listening!