## Bridging Functional and Architectural Aspects of Controller Design in Cyber-Physical System

EECS Department, UC Berkeley 6/7/2013

## Gap between Function and Architecture

- Function: describe the functionality of the design

- Behaviors that the system should implement

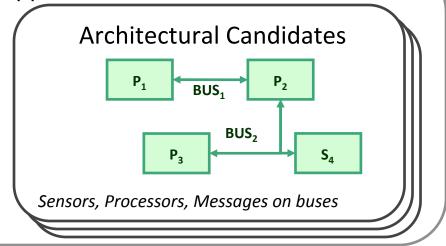

- Architecture: provides various platform targets (configurations of resources that implement certain functions)

- The functionality is modeled on high abstraction level with heterogeneous MoCs

- High level abstraction without implementation details

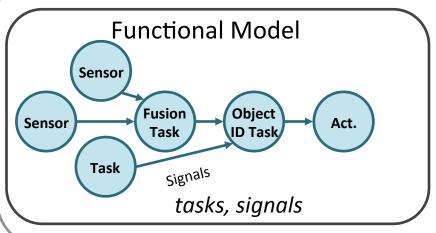

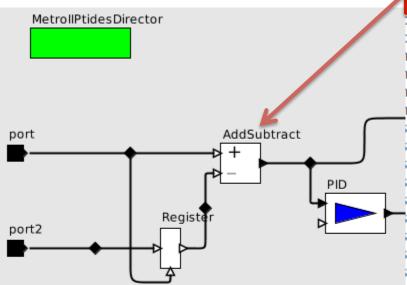

## A Functional Model without Implementation Details

# Functional Behaviors are Affected by Implementation Details

## Need New Methods & Tools for Bridging Functional & Architectural

- Aspects

Approach 1: refine functional model by adding implementation details

- E.g. add bus model

- Potential problems:

- The model becomes complicated to understand and modify

- Environment/language for modeling function is not suitable for architecture.

- Semantic restriction: difficult to model complex architecture in functional environment

- Approach 2: construct the function using architectural primitives

- E.g. programming language

- Potential problems:

## Need New Methods & Tools for Bridging Functional & Architectural Aspects

- Approach 3: make assumptions (contracts) that decouple the function and architecture

- E.g. assume a bounded communication delay

- Potential problems:

- Making 'appropriate' assumptions is hard

- Assumptions of the functional model about the architecture significantly impact the Software/ Hardware implementation

- Inappropriate assumptions may restrict the design choices and lead to costly or infeasible architecture

### **Aspect-Oriented Modeling**

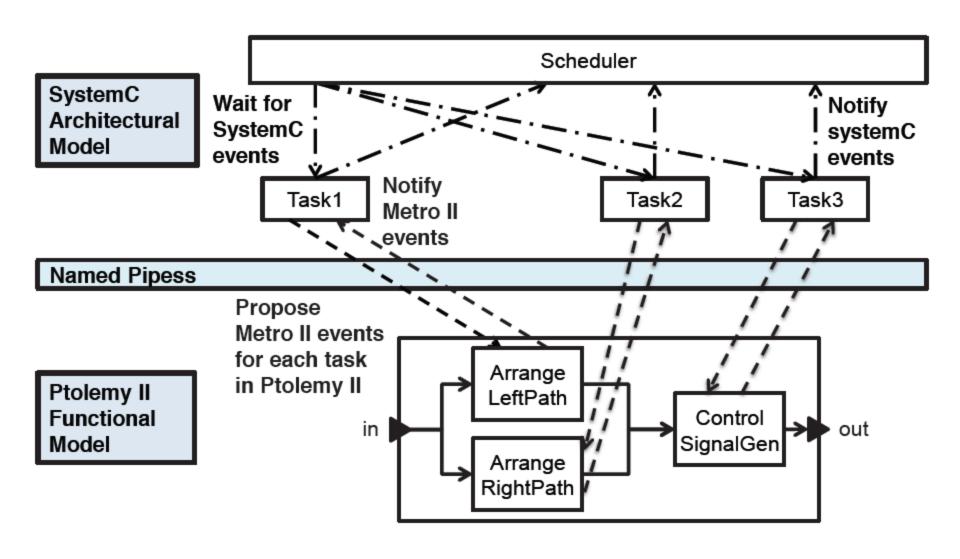

Joint modeling of implementation architecture and functional design to enable effective architecture exploration and assessment of the behavioral consequences of architectural choices.

- What is the performance? How this modifies the behavior? Does this satisfy the vertical contract?

- Investigate different design choices for the same functional model

## Aspect-Oriented Modeling

- Map functional and architectural models without significant changes

- Enable co-simulation and performance estimation of the mapped model

- Provide interfaces to explore design and performance Mapping, parameters, ...

- **ரஜர்ஞுரிந்**ce estimations

Simulation of Mapped Model

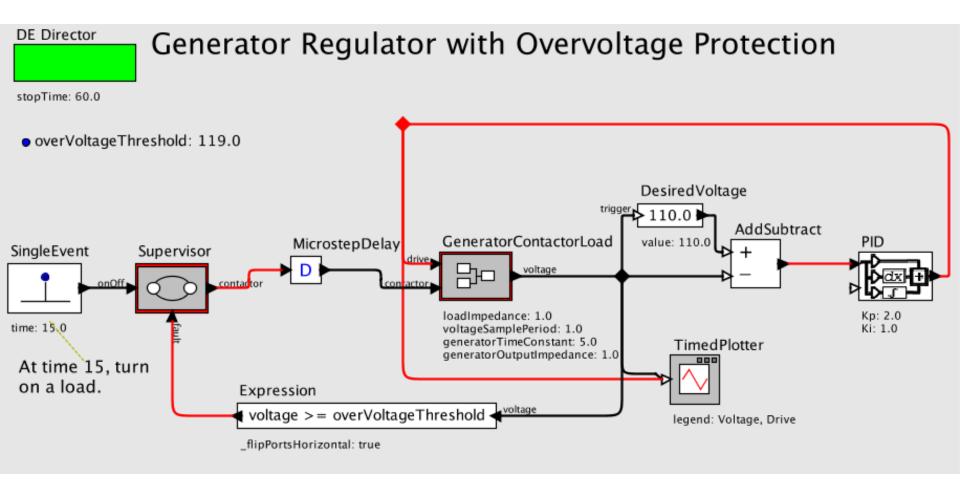

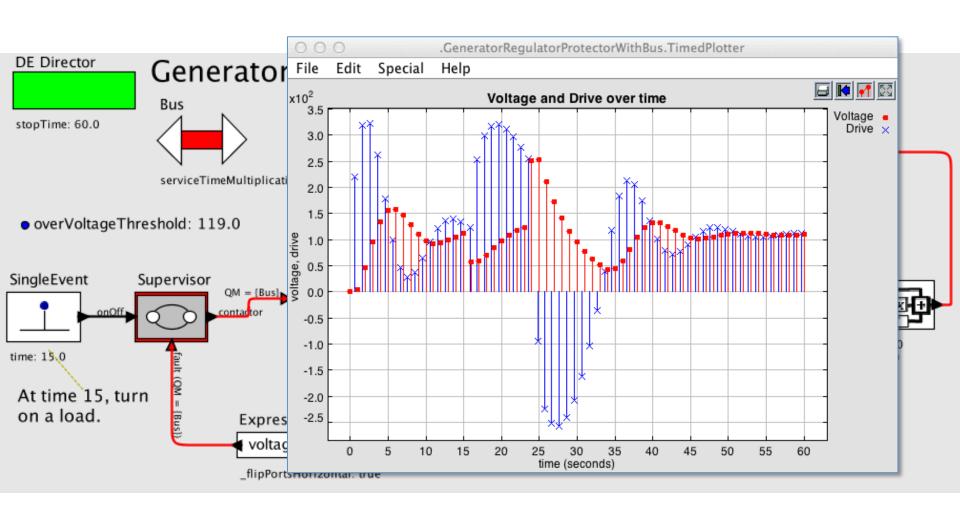

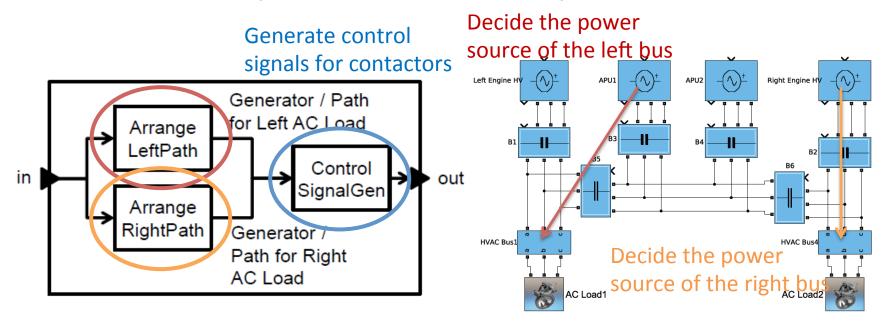

## Example 1: Simplified BCU Controller

- Decide the power sources for AC buses

- Input: fault signals of power sources and contactors

- Output: control signals for contactors

- Constraint: power sources are never paralleled

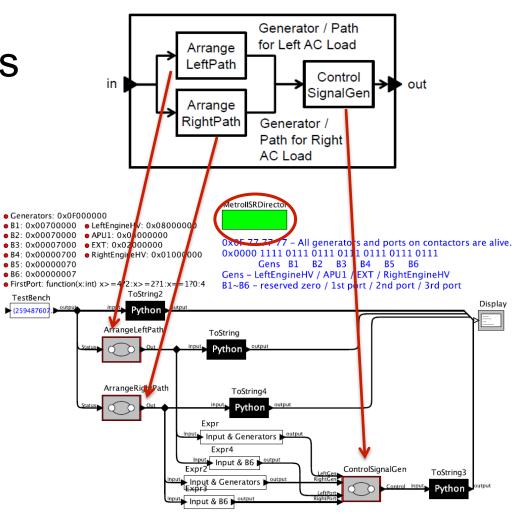

## Functional Model in Ptolemy

Model each part as a FSM

Compose FSMs into a Synchronou Reactive (SR) Model

SR Director is modified to make

## Map to Arch Model in SystemC

## Preliminary Co-simulation Results

#### Candidate 1

High-speed single processor

#### Candidate 2

- Slow-speed dual processors

- low synchronization overhead

#### Candidate 3

- Medium speed dual processors

- high synchronization

| Parameters                     |     | Candidate |     |     |

|--------------------------------|-----|-----------|-----|-----|

|                                |     | 1         | 2   | 3   |

| Scheduling overhead (ns)       |     | 10        | 10  | 10  |

| Execution Time (ns)            | ALP | 40        | 60  | 50  |

|                                | ARP | 45        | 65  | 55  |

|                                | CSG | 25        | 35  | 30  |

| Synchronization overhead (ns)  |     | 0         | 5   | 15  |

| Parallelization of ALP and ARP |     | No        | Yes | Yes |

| Total execution time (ns)      |     | 775       | 800 | 750 |

ALP: left controller

ARP: right controller

CSG: control signal generator

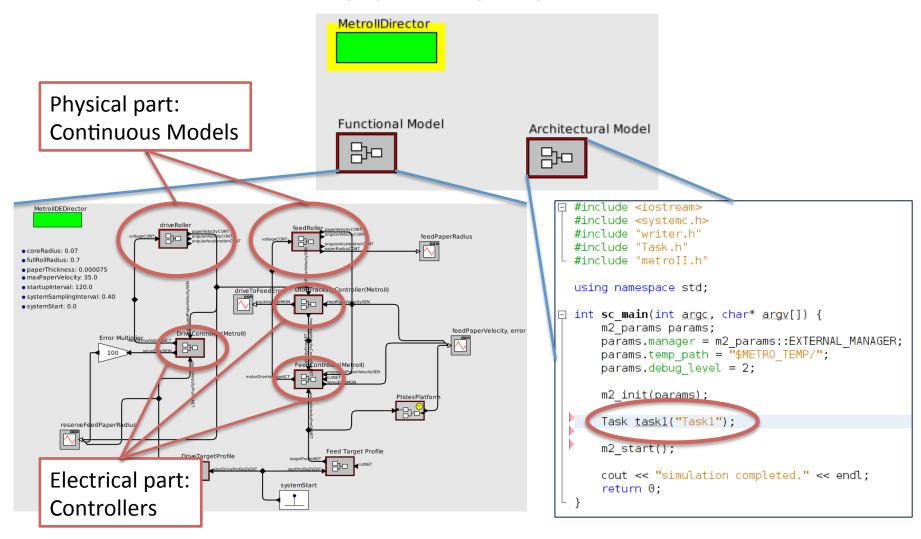

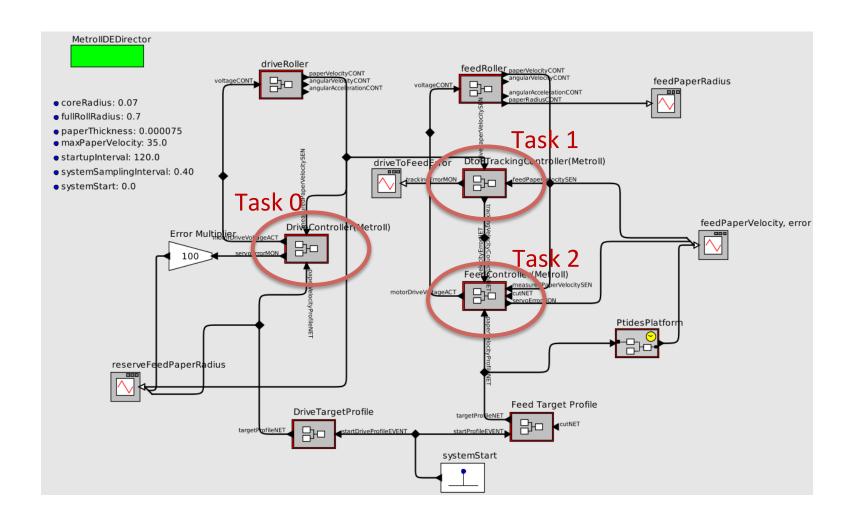

## Example 2: printingpress controller

### Mapping Configuration

#### Ptides MoC

The controller is a PID controller that minimizes the <code>(.Const2.FIRE\_END,Task2.Const.End)</code> between the target velocity profile and the measure .PID.FIRE\_BEGIN, Task2.PID.Begin

:s.Register.FIRE\_BEGIN,TaskO.Register.Begin s.Register.FIRE END.TaskO.Register.End s.AddSubtract.FIRE BEGIN.Task0.AddSubtract.Begin s.AddSubtract.FIRE\_END,Task0.AddSubtract.End s.PID.FIRE BEGIN.TaskO.PID.Begin s.PID.FIRE\_END,Task0.PID.End Contents.AddSubtract.FIRE\_BEGIN,Task1.AddSubtract.Begin Contents.AddSubtract.FIRE\_END,Task1.AddSubtract.End Contents.PID.FIRE\_BEGIN,Task1.PID.Begin Contents.PID.FIRE\_END,Task1.PID.End .Register.FIRE\_BEGIN,Task2.Register.Begin ..Register.FIRE\_END,Task2.Register.End ..Register2.FIRE\_BEGIN,Task2.Register.Begin ..Register2.FIRE\_END,Task2.Register.End .AddSubtract.FIRE\_BEGIN,Task2.AddSubtract.Begin .AddSubtract.FIRE\_END,Task2.AddSubtract.End .AddSubtract2.FIRE BEGIN, Task2.AddSubtract.Begin .AddSubtract2.FIRE END, Task2.AddSubtract.End ..Const.FIRE BEGIN, Task2.Const.Begin .Const.FIRE END, Task2.Const.End ..Const2.FIRE BEGIN, Task2.Const.Begin

..PID.FIRE END,Task2.PID.End

The register actor is required since the sensor sampling is not necessary. frequency as the frequency of receipt of profile information.

## Mapping Configuration

### Round-Robin Scheduling

- Architectural model

- Designed in a language and environment that are comfortable for architecture designer

- Example 1: RR scheduling

```

Task* 0S::next_task_to_run() {

if (_ready_task_list.empty()) {

return NULL;

}

Task* next_task = _ready_task_list.front()

ready_task_list.pop_front();

return next_task;

}

```

```

500 ms: Task0.Register begins

500005 us: TaskO.Register ends

500005 us: Task2.Register begins

500010 us: Task2.Register ends

500010 us: TaskO.AddSubtract begins

500012 us: Task0.AddSubtract ends

500012 us: Task2.AddSubtract begins

500014 us: Task2.AddSubtract ends

500014 us: TaskO.PID begins

500029 us: Task0.PID ends

500029 us: Task2.Register begins

500034 us: Task2.Register ends

500034 us: Task2.AddSubtract begins

500036 us: Task2.AddSubtract ends

500036 us: Task2.PID begins

500051 us: Task2.PID ends

500051 us: Task2.Const begins

500053 us: Task2.Const ends

```

```

800 ms: Task1.AddSubtract begins

800002 us: Task1.AddSubtract ends

800002 us: Task2.Register begins

800007 us: Task2.Register ends

800007 us: Task0.Register begins

800012 us: Task0.Register ends

800012 us: Task1.PID begins

800027 us: Task1.PID ends

800100 us: Task2.Register begins

800105 us: Task2.Register ends

```

## Priority-based Scheduling

Example 1: priority-bas

```

Task* 0S::next_task_to_run() {

if (_ready_task_list.empty()) {

return NULL;

}

// Task* next_task = _ready_task_list.front();

// _ready_task_list.pop_front();

list<Task *>::iterator it_highest_priority = _refor (list<Task *>::iterator it=_ready_task_list if ((*it)->priority() > (*it_highest_priority it_highest_priority = it;

}

}

Task * next_task = (*it_highest_priority);

_ready_task_list.erase(it_highest_priority);

return next_task;

}

```

```

500 ms: TaskO.Register begins

500005 us: TaskO.Register ends

500005 us: Task0.AddSubtract begins

500007 us: Task0.AddSubtract ends

500007 us: TaskO.PID begins

500022 us: Task0.PID ends

500022 us: Task2.Register begins

500027 us: Task2.Register ends

500027 us: Task2.AddSubtract begins

500029 us: Task2.AddSubtract ends

500029 us: Task2.Register begins

500034 us: Task2.Register ends

500034 us: Task2.AddSubtract begins

500036 us: Task2.AddSubtract ends

500036 us: Task2.PID begins

500051 us: Task2.PID ends

it++)

500051 us: Task2.Const begins

500053 us: Task2.Const ends

800 ms: TaskO.Register begins

800005 us: TaskO.Register ends

800005 us: Task1.AddSubtract begins

800007 us: Task1.AddSubtract ends

800007 us: Task1.PID begins

800022 us: Task1.PID ends

800022 us: Task2.Register begins

800027 us: Task2.Register ends

800100 us: Task2.Register begins

800105 us: Task2.Register ends

```

### Performance Annotation

The basic performance annotation can be suptomized in a countrie.

customized in a csv file

| Register               | 5 SC_US            |

|------------------------|--------------------|

| DiscreteClock          | 1SC_US             |

| CurrentTime            | 1 SC_US            |

| Scale                  | 5 SC_US            |

| TrigFunction           | 10 SC_US           |

| Const                  | 2 SC_US            |

| AddSubtract            | 2 SC_US            |

|                        |                    |

| BooleanSwitch          | 5 SC_US            |

| BooleanSwitch<br>Merge | 5 SC_US<br>5 SC_US |

| ~~~~~~~~~              |                    |

| Merge                  | 5 SC_US            |

| Merge<br>LogicalNot    | 5 SC_US<br>2 SC_US |

500005 us: TaskO Register ends 500005 us: Tasku.AddSubtract begins 500007 us: Task0 AddSubtract ends 500007 us: TaskO.PID begins 500022 us: Task0.PID ends 500022 us: Task2.Register begins 500027 us: Task2.Register ends 500027 us: Task2.AddSubtract begins 500029 us: Task2.AddSubtract ends 500029 us: Task2.Register begins 500034 us: Task2.Register ends 500034 us: Task2.AddSubtract begins 500036 us: Task2.AddSubtract ends 500036 us: Task2.PID begins 500051 us: Task2.PID ends 500051 us: Task2.Const begins 500053 us: Task2.Const ends

### Summary

- A simulation-based architecture exploration framework

- Separate function/architecture models

- Change mapping without significantly modifying models

- Evaluate performance,

- Explore architectural candidates and 'discover' new architectures

### **THANK YOU**